High-speed designs demand precise signal transmission to ensure optimal performance. Poor signal integrity can lead to issues like bit errors, data corruption, and even system failure in critical applications. Factors such as dielectric constant, loss tangent, and insertion loss significantly impact signal quality. By using signal integrity simulation, you can identify and address these challenges early. This proactive approach helps maintain clean signal edges, minimize reflections, and optimize transmission lines, ensuring reliable and efficient designs.

Key Takeaways

Signal integrity is very important for fast designs. It helps send data correctly and avoids errors or damage.

Use early simulations to find design problems quickly. This saves time and avoids expensive fixes later.

Use tools like SPICE and IBIS-AMI to check signals. These tools show problems like noise or timing issues before they happen.

Look at eye diagrams to check signal quality. A clear eye means good signals, but a messy eye shows problems to fix.

Fix noise and timing issues by improving PCB design and matching signal paths. These steps make signals clearer and systems work better.

Understanding Signal Integrity in High-Speed Designs

What is Signal Integrity?

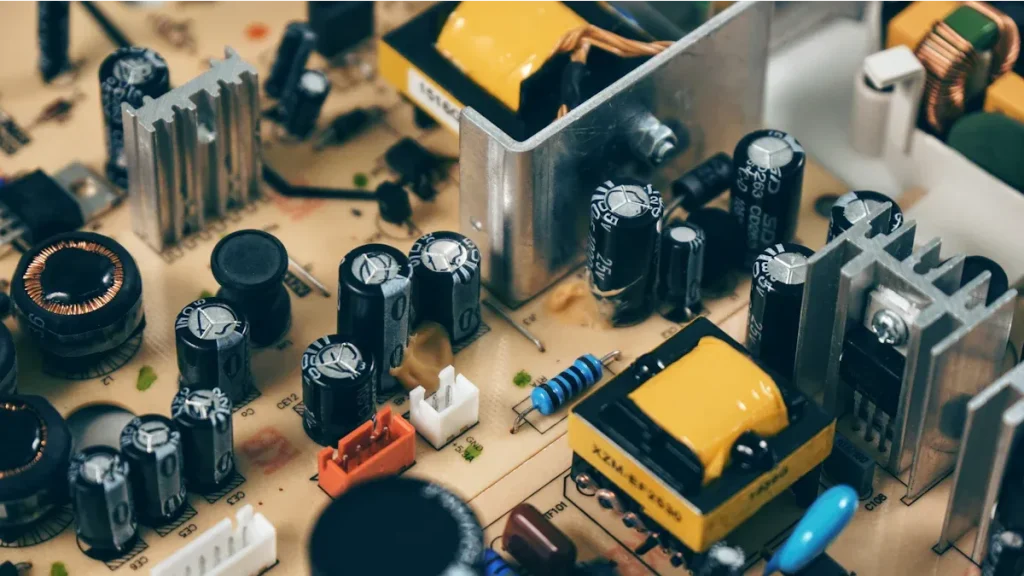

Signal integrity refers to the ability of a signal to maintain its quality and accuracy as it travels through a high-speed system. In high-frequency hardware design, preserving signal integrity ensures reliable data transmission and optimal performance. Several principles guide this process: maintaining impedance matching, minimizing noise, and reducing signal distortions. These factors help prevent issues like data corruption and communication errors, which are critical in applications such as medical devices and automotive systems.

To achieve robust signal integrity, you must focus on proper routing, impedance control, and noise reduction. For example, managing simultaneous switching noise (SSN) and performing decoupling analysis can significantly improve the performance of your power distribution network (PDN). By integrating signal and power integrity analysis, you can ensure that high-frequency signals retain their quality during transmission.

Challenges in High-Speed Systems

Crosstalk and Its Impact

Crosstalk occurs when signals from adjacent conductive paths interfere with each other. This interference, known as near-end crosstalk (NEXT) or far-end crosstalk (FEXT), can degrade signal clarity. In densely packed connectors, crosstalk becomes a significant challenge, leading to reduced signal integrity and potential data errors.

Jitter and Timing Variations

Jitter refers to the deviation of signal timing from its ideal position. It disrupts synchronization, causing timing errors in high-speed systems. For instance, cycle-to-cycle jitter measures variations between consecutive clock periods, while timing interval error (TIE) highlights discrepancies between observed and expected clock edges. These variations can severely impact system reliability.

Signal Attenuation and Reflection

Signal attenuation reduces signal strength due to absorption and reflection during transmission. Impedance mismatches exacerbate this issue, causing energy loss and signal distortion. High-frequency signals are particularly vulnerable, as they experience greater resistance and attenuation, compromising overall performance.

Importance of Signal Integrity in High-Speed Designs

Maintaining signal integrity is essential for preventing bit errors, data corruption, and system failures. Impedance mismatches, crosstalk, and electromagnetic interference (EMI) can disrupt signal clarity, especially in high-density environments. By addressing these challenges, you can ensure accurate transmission of high-frequency signals, minimize degradation, and enhance system reliability. Signal integrity analysis plays a vital role in achieving these goals, making it a cornerstone of high-frequency hardware design.

Tools and Techniques for Signal Integrity Analysis

Simulation Tools for Signal Integrity

Software Tools (e.g., SPICE, IBIS-AMI)

Advanced signal integrity software plays a crucial role in analyzing and optimizing high-speed designs. Tools like SPICE and IBIS-AMI are widely used for signal integrity analysis. SPICE models simulate circuit behavior with high accuracy, helping you predict potential issues such as reflections and crosstalk. This allows you to address problems early in the design phase, saving time and costs. On the other hand, IBIS-AMI models excel in high-speed interconnect modeling. They simulate complex behaviors like equalization and clock recovery efficiently, without revealing proprietary information. While SPICE offers unmatched precision, it can be computationally intensive for long simulations. IBIS-AMI provides a faster alternative for analyzing high-speed channels.

Hardware Tools for Validation

Hardware tools complement software simulations by validating real-world performance. Oscilloscopes and vector network analyzers (VNAs) are essential for measuring parameters like impedance, jitter, and crosstalk. These tools help you verify the accuracy of your simulations and ensure that your design meets performance requirements. Real-time eye diagrams generated using these tools provide valuable insights into signal quality, enabling you to identify and resolve issues effectively.

Key Techniques in Signal Integrity Analysis

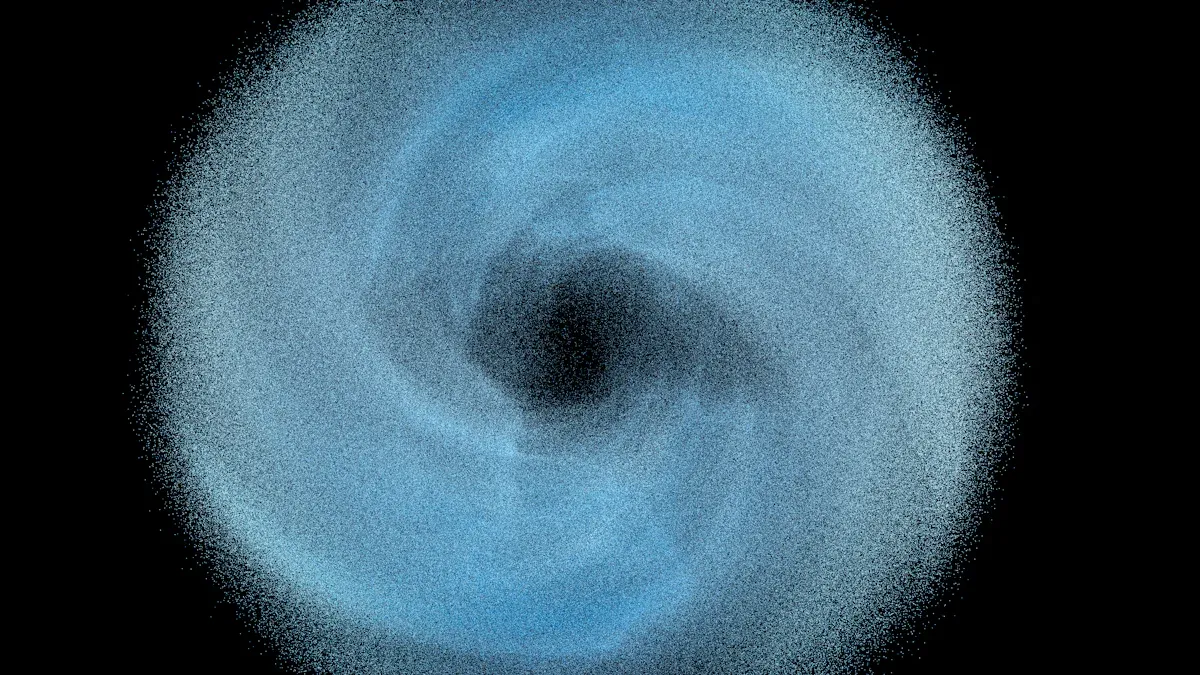

Eye Diagrams and Their Role

Real-time eye diagrams are indispensable for evaluating signal quality. They visually represent how much a signal degrades as it travels from the transmitter to the receiver. A closed eye diagram indicates potential signal integrity problems, such as excessive noise or jitter. By analyzing these diagrams, you can identify timing errors and amplitude variations, ensuring optimal system performance.

Electromagnetic Simulation

Electromagnetic simulations help you understand how transmission lines and components interact with high-frequency signals. Techniques like mixed-mode S-parameters and time-domain reflectometry (TDR) pinpoint the root causes of signal degradation. These simulations provide a deeper understanding of your design’s electromagnetic behavior, enabling you to optimize it for better performance.

Modeling Methods (DFE, FFE, CTLE)

Decision Feedback Equalization (DFE), Feed-Forward Equalization (FFE), and Continuous-Time Linear Equalization (CTLE) are advanced techniques used in signal integrity analysis. These methods enhance signal quality by compensating for losses and distortions in high-speed channels. Incorporating these techniques into your design ensures reliable data transmission and improved system performance.

Selecting the Right Tools for Your Design

Choosing the right tools for signal integrity analysis depends on your design requirements. Consider factors like signal quality, crosstalk, and timing accuracy. Advanced signal integrity software, such as SPICE and IBIS-AMI, is ideal for pre-layout and post-layout analyses. For real-world validation, hardware tools like oscilloscopes and VNAs are indispensable. Evaluate your design’s complexity and performance goals to select the most suitable tools.

Implementing Signal Integrity Simulations

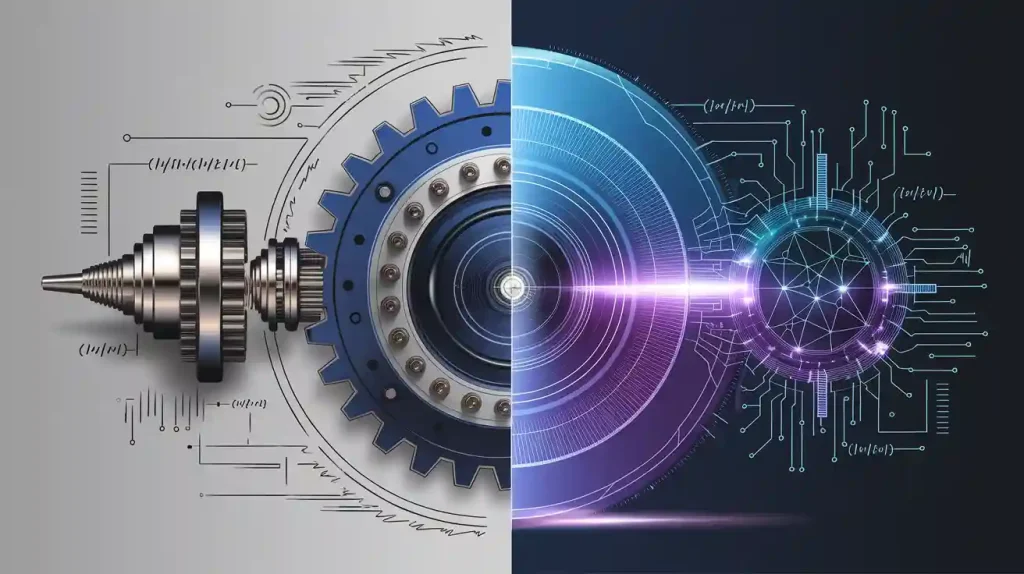

Pre-Layout and Post-Layout Simulations

Exploring Design Space in Pre-Layout

Pre-layout simulations allow you to validate your design before finalizing the PCB layout. These simulations focus on early-stage decisions, such as selecting trace widths, stack-up configurations, and impedance targets. By exploring the design space, you can identify potential issues like signal loss or crosstalk and make adjustments before committing to a physical layout. This proactive approach saves time and reduces costly revisions later in the design process.

Verifying Geometry-Dependent Issues in Post-Layout

Post-layout simulations analyze the finalized PCB layout to uncover geometry-dependent issues. These include parasitic effects, impedance mismatches, and reflections caused by the physical arrangement of high-speed PCB traces. Post-layout analysis provides a detailed representation of your design’s real-world behavior, ensuring that your signal integrity measurement solution meets performance requirements.

Setting Up the Simulation Environment

Preparing Design Files and Models

Preparing your design files is a critical step in setting up the simulation environment. Modify the geometry of your CAD designs to enhance their suitability for analysis. Ensure that the import process is associative so simulation settings remain intact even after reimporting the CAD file. This preparation ensures accurate and efficient simulations.

Configuring Simulation Parameters

Configuring simulation parameters involves several steps. First, simulate the channel using an eye diagram to assess signal degradation. Next, locate the root cause of degradation with tools like mixed-mode S-parameters and time-domain reflectometry (TDR). Finally, perform post-layout analyses to examine parasitics and geometry-dependent issues. These steps help you create a robust simulation environment.

Running and Validating Simulations

Simulating Signal Paths

Simulating signal paths helps you evaluate how signals travel through your design. Use models like IBIS to represent component behavior accurately. Simulate the channel with an eye diagram to visualize signal quality and identify potential issues. This step ensures that your design supports reliable data transmission.

Testing for Crosstalk and Jitter

Testing for crosstalk and jitter is essential for maintaining signal integrity. Crosstalk can degrade signal clarity, while jitter disrupts timing accuracy. Use tools like TDR and mixed-mode S-parameters to locate the root causes of these issues. Perform thorough analyses during both pre- and post-layout stages to address problems early and optimize your design.

Interpreting Signal Integrity Simulation Results

Analyzing Eye Diagrams

Identifying Signal Quality Issues

Eye diagram analysis is a powerful tool for evaluating signal quality in high-speed designs. You can use it to assess critical factors such as noise levels and timing errors. By visualizing the signal’s behavior, you can identify issues like excessive jitter or amplitude variations. Noise analysis helps you pinpoint sources of interference, enabling you to implement effective mitigation strategies. Additionally, compliance testing ensures that your signals meet industry standards by comparing them against predefined mask limits.

Tip: A well-formed eye diagram with a wide-open “eye” indicates good signal integrity, while a closed or distorted eye suggests potential problems.

Measuring Eye Height and Width

Eye height and width are key metrics in eye diagram analysis. Eye height measures the vertical opening of the eye, reflecting the signal’s noise margin. A larger eye height indicates better noise immunity. Eye width, on the other hand, represents the horizontal opening and correlates with timing accuracy. Narrow eye width often signals timing issues, such as jitter. By measuring these parameters, you can evaluate the overall quality of your signal and make necessary adjustments to improve performance.

Addressing Common Signal Integrity Problems

Mitigating Crosstalk

Crosstalk occurs when signals on adjacent traces interfere with each other, leading to data errors. You can mitigate this issue by:

Ensuring proper impedance matching to reduce reflections.

Optimizing PCB layout by increasing trace spacing and minimizing parallel runs.

Using multiple ground planes to reduce coupling between traces.

Reducing Jitter

Jitter disrupts timing accuracy and can cause sampling errors. To address jitter, you should:

Simulate the channel using an eye diagram to identify timing variations.

Use tools like time-domain reflectometry (TDR) to locate the root causes.

Optimize trace lengths and ensure consistent impedance throughout the design.

Optimizing Designs Based on Simulation Insights

Signal integrity analysis provides valuable insights for optimizing your design. For instance, placing signal layers adjacent to continuous ground planes minimizes noise and improves signal quality. Symmetrical stack-up designs prevent warping and ensure consistent performance. By addressing issues like crosstalk and jitter during the design phase, you can enhance reliability and reduce costly revisions. Simulation tools like mixed-mode S-parameters allow you to pinpoint degradation sources and refine your design for better results.

Benefits of Signal Integrity Analysis for High-Speed Designs

Enhancing System Performance

Signal integrity analysis plays a crucial role in improving the performance of high-speed systems. By understanding how signals behave within your design, you can optimize routing, stack-up, and component placement. This ensures that signals remain clean and reliable, reducing the risk of errors or failures.

Signal integrity analysis provides insights into signal interactions, helping you refine your design for better efficiency.

Enhanced signal quality minimizes noise and distortion, ensuring accurate data transmission.

Optimized designs lead to improved system performance and reduced debugging efforts.

When you address these factors early, your high-speed digital PCB can achieve superior performance, even in demanding applications.

Improving Reliability and Longevity

Reliable systems depend on clean signals and consistent performance. Signal integrity analysis helps you identify and resolve issues that could degrade signal quality. For example, excessive heat can cause impedance variations along transmission lines, leading to reflections and signal loss. By addressing these problems, you ensure reliable data transmission and extend the lifespan of your design.

Unchecked signal integrity issues often result in bit errors, data corruption, or even system failure. Effective design practices, such as impedance matching and proper termination, mitigate these risks. Signal integrity simulations also help you achieve clean signals without overshoot or ringback, further enhancing reliability.

Reducing Costs Through Early Issue Detection

Detecting and resolving signal integrity problems early in the design phase saves significant costs. Pre-layout simulations allow you to explore design options and address potential issues before committing to a physical layout. This proactive approach reduces the need for costly revisions and shortens development cycles.

By ensuring your design meets performance requirements from the start, you avoid expensive rework and production delays. Early detection of issues like crosstalk, jitter, and signal attenuation ensures your high-speed digital PCB performs reliably, minimizing long-term maintenance costs.

Signal integrity simulation is essential for ensuring reliable performance in high-speed designs. By leveraging advanced tools like SPICE and IBIS-AMI, you can analyze critical factors such as impedance matching, crosstalk, and timing accuracy. Techniques like pre-layout and post-layout simulations allow you to identify potential issues early, saving time and reducing costs.

Proactive analysis enhances design efficiency by optimizing routing and component placement. It also improves signal quality, ensuring accurate data transmission and minimizing errors. With these insights, you can create robust designs that meet performance requirements and maintain long-term reliability.

Tip: Always validate your design with both software simulations and hardware tools to achieve the best results.

FAQ

1. What is the purpose of signal integrity simulation?

Signal integrity simulation helps you predict and resolve issues like crosstalk, jitter, and signal loss in high-speed designs. It ensures your signals remain clear and reliable, improving performance and reducing the risk of errors or failures.

Tip: Use simulations early in the design process to save time and costs.

2. How do pre-layout and post-layout simulations differ?

Pre-layout simulations explore design options before finalizing the PCB layout. They focus on factors like trace width and impedance. Post-layout simulations analyze the actual PCB layout to identify geometry-dependent issues, such as parasitics and reflections.

Note: Both simulations are essential for ensuring robust signal integrity.

3. Which tools are best for signal integrity analysis?

Software tools like SPICE and IBIS-AMI are ideal for simulations. Hardware tools, such as oscilloscopes and vector network analyzers (VNAs), validate real-world performance. Choose tools based on your design’s complexity and requirements.

Emoji Insight: 🛠️ Combine software and hardware tools for the best results.

4. How can you reduce crosstalk in high-speed designs?

You can reduce crosstalk by increasing trace spacing, minimizing parallel runs, and using ground planes. Proper impedance matching also helps prevent reflections that worsen crosstalk.

Pro Tip: Optimize your PCB layout to minimize interference between traces.

5. Why is eye diagram analysis important?

Eye diagrams visually show signal quality. A wide-open “eye” indicates good signal integrity, while a closed or distorted eye suggests issues like jitter or noise. Measuring eye height and width helps you evaluate noise margins and timing accuracy.

Reminder: Regularly analyze eye diagrams to ensure reliable data transmission.