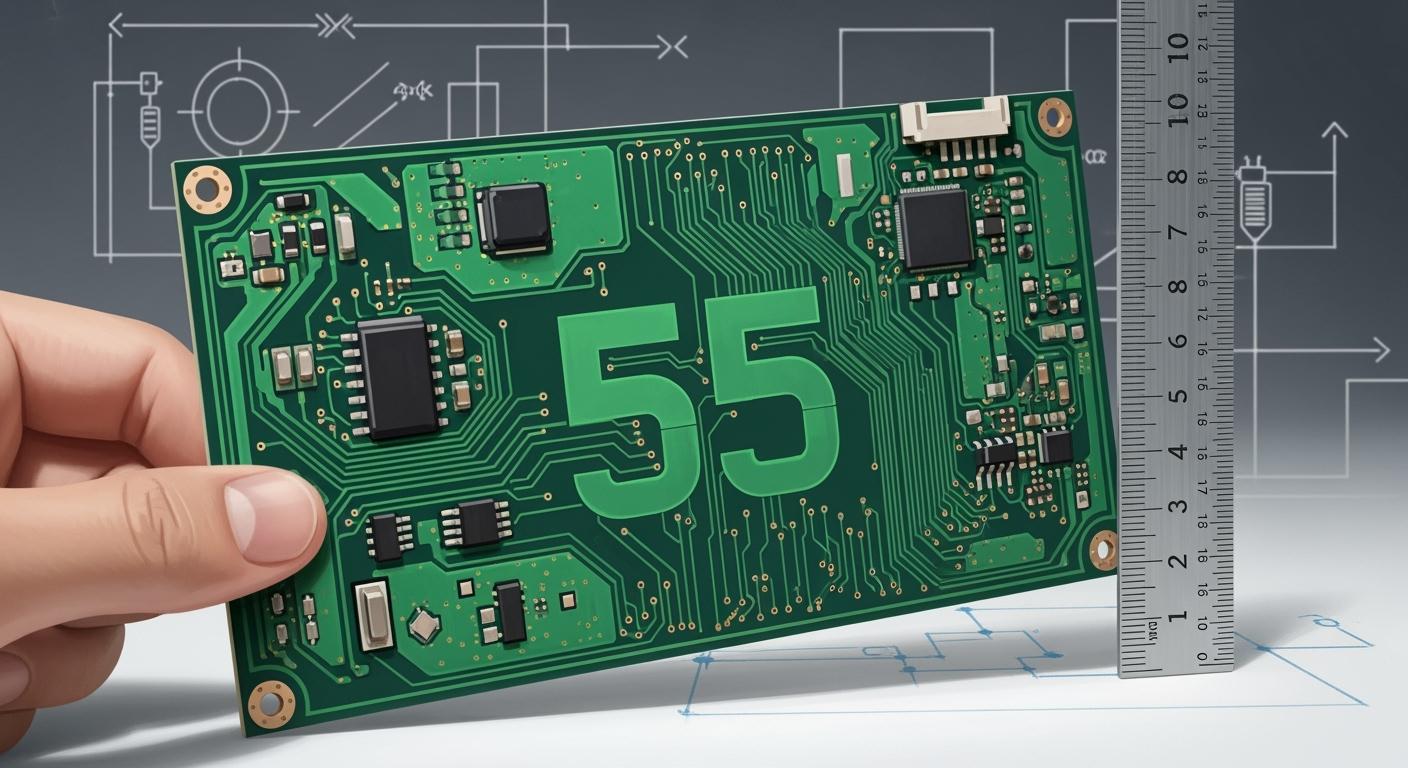

在PCB設計中,您可以使用「55法則」來保持訊號走線之間的間距至少為其寬度的五倍。這項原則在高速電路中尤其重要。遵循此法則可以提高訊號完整性,並減少電磁幹擾(EMI)和串擾等問題,從而獲得更清晰的訊號和更可靠的性能。

關鍵要點

55 法則指出,訊號線之間的距離至少應為其寬度的五倍。這有助於保持訊號強度並減少干擾。

加寬高速訊號的走線可以降低電阻。這樣可以保持訊號強度,並防止雜訊幹擾電路正常運作。

高速線路應盡可能短,避免使用尖角。這樣可以降低訊號損耗,使訊號路徑更加清晰。

在實際製作之前,使用模擬工具檢查你的設計。這能及早發現問題,並改善設計。

和你的PCB製造商溝通,了解他們的能力範圍。了解他們的限制有助於你設計出適合他們的產品。

PCB設計中的55條規則概述

什麼是55法則?

您可以使用「55法則」來幫助您在PCB上合理佈置和調整走線。這條法則指出,走線之間的間距至少應為其寬度的五倍。遵循這條法則可以避免高速電路中出現不必要的干擾。如果走線間距夠大,訊號就不會互相干擾,訊號也能更順暢地從一個位置傳送到另一個位置。 「55法則」有助於您的PCB更好地處理高速訊號。

技術基礎與起源

你應該了解55法則對訊號品質的重要性。其核心思想是控制訊號的環路位置以及走線的寬度和間距。遵循55法則可以降低雜訊和電壓尖峰等問題,也能防止訊號與電源走線混雜,從而避免產生錯誤。

提示:55 法則可以讓你的 PCB 運作得更好,尤其是在處理快速訊號時。

下表列出了支持PCB設計中55法則的科學原理:

原則 | 解釋 |

|---|---|

最小化寄生電感 | 較短的電源走線使迴路面積變小,這有助於在高 di/dt 電路中防止電壓振鈴。 |

高電流走線使用外層 | 外層散熱效果更好;使用更多過孔有助於在高電流下散熱。 |

防止訊號-功率走線耦合 | 訊號走線應與電源線垂直交叉,以防止電容耦合並保持訊號純淨。 |

每項原則都有助於保持訊號的強度和清晰度。透過避免走線過度繞環,可以降低寄生電感。對於高電流走線,可以使用外層材料來幫助散熱和散熱。將訊號走線與電源走線分開,可防止不必要的混疊。所有這些步驟都有助於「55法則」發揮作用,並帶來更好的結果。 高速PCB設計.

高速PCB設計的重要性

訊號完整性影響

在高速PCB設計中,保持訊號的清晰度和強度至關重要。 55法則透過確保每條訊號線與其他訊號線保持足夠的距離來幫助您實現這一點。遵循此法則,可以使訊號路徑更短更直接,從而防止訊號受到雜訊幹擾或強度衰減,並避免訊號反射導致錯誤。

55 法則對於高速 PCB 設計至關重要,因為它旨在最大限度地減少訊號環路面積。這在處理高時脈頻率或快速訊號上升時間時尤其重要。較小的環路面積意味著訊號更不容易受到雜訊幹擾。遵循此法則可以顯著提升 PCB 的效能。

注意:乾淨的訊號路徑意味著更少的故障和更可靠的電路。

電磁幹擾與串擾抑制

您需要避免PCB板中出現電磁幹擾(EMI)和串擾等問題。 EMI是指電磁幹擾。串擾是指一個訊號影響附近另一個訊號。兩者都會導致電路故障或異常行為。

您可以使用「55法則」來降低這些風險。保持線路之間的距離,可以降低訊號跳到其他線路的機率。同時,也能有效防止外部噪音幹擾訊號。這使得您的高速PCB設計更加可靠。

遵循55法則,您可以獲得以下好處:

降低訊號錯誤風險

減少隨機重置或故障

整體表現更佳

透過保持訊號分離且強度高,可以改進設計。這樣就能製造出即使在高速運轉時也能良好運作的PCB。

在PCB佈局中應用55法則

線條寬度和間距指南

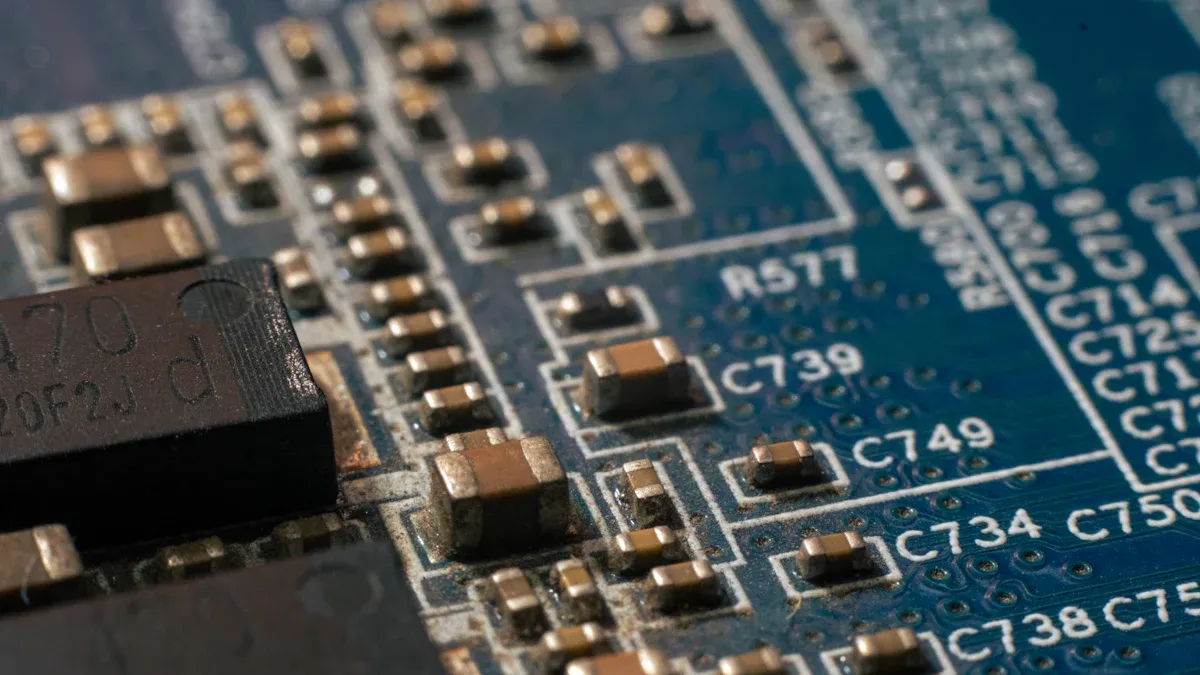

您必須選擇合適的走線寬度和間距。 55 法則規定走線之間的距離應為其寬度的五倍。這樣可以確保每個訊號免受雜訊和乾擾。對於快速訊號,應使用更寬的走線以降低電阻。更寬的走線有助於保持訊號強度。小型元件至少需要 0.5 毫米的間距。大型元件需要 1-2 毫米的間距。設計規則檢查可以幫助您發現間距錯誤。

提示:盡量以 45 度角佈線。這樣可以使訊號路徑更平滑,並防止反射。

一個簡單的表格可以幫助你記住該做什麼:

追蹤類型 | 建議寬度 | 最小間距(55 規則) |

|---|---|---|

高速訊號 | 0.2 mm | 1.0 mm |

功率追蹤 | 0.5 mm | 2.5 mm |

模擬信號 | 0.2 mm | 1.0 mm |

層疊策略

您可以在PCB上使用更多層來改善訊號傳輸。將接地層放置在高速訊號層旁邊,這樣可以降低雜訊並保持訊號純淨。將類比訊號和數位訊號放在不同的層上,可以防止串擾並優化設計。在電源層上使用寬走線以確保良好的電源傳輸。將功耗相同的元件放在一起。

注意:差分訊號對的走線長度務必保持一致,這樣可以確保訊號匹配。

訊號路由最佳實踐

在PCB上佈線時,請務必仔細規劃訊號線。高速走線要短而直。避免使用尖角,因為這會損害訊號。使用仿真工具檢查問題。將發熱元件遠離重要的訊號路徑。使用導熱過孔將熱量從關鍵位置散發出去。

以下是一些常見錯誤以及如何避免這些錯誤:

零件間距錯誤:請使用設計規則檢查。

不良的走線佈局:保持走線寬度相同,並使用 45 度角。

遺忘 信號完整性使用接地平面並匹配走線長度。

功率輸出較弱:使用寬走線並將相似的部件分組。

無需處理熱量:使用導熱過孔和智慧元件佈局。

缺少製造規範:請遵循標準設計規範。

按照以下步驟操作,您可以製作出堅固可靠的PCB板。 55法則有助於保持訊號清晰,確保您的設計安全。

高速PCB設計面臨的挑戰

密集元件放置

在高速PCB上遵循55規則會面臨許多挑戰。元件密集佈局使得走線之間難以保持足夠的間距。元件間距過近會導致焊接缺陷增多,進而增加重工和維修次數。此外,如果某些元件在焊接過程中阻擋熱量,也會造成連接強度不足的風險。間距較佳的電路板使用壽命較長,能夠承受較多的熱循環次數。

緊湊的佈局可能會因焊接問題而使返工率增加 37%。

高大的部件會產生熱陰影,導致連接處強度不足,在壓力測試中容易斷裂。

良好的間距可以使電路板承受三倍的加熱和冷卻循環。

設計電路圖時,請務必為每個訊號預留足夠的空間。這有助於保持電路板的強度和可靠性。

管理差分對

在高速訊號設計中,差分對的佈線需要格外謹慎。差分對承載兩個訊號,這兩個訊號必須保持緊密相鄰且長度匹配。如果間距不合適,可能會造成訊號遺失。 訊號品質你應該保持兩條走線之間的間距很小,同時也要讓其他訊號遠離它們。這有助於避免串擾,並保持高速訊號的純淨。

盡量使用多層板來分離訊號層和接地層。這樣可以更好地控制走線路徑,並有助於遵循 55 規則。務必檢查一對走線的長度是否相同,以確保訊號平衡。

克服製造限制

你可能會遇到 您的PCB製造商設定的限制有些工廠無法製作極細的走線或極小的間距。這會導致難以遵循55規則,尤其是在高速設計中。您應該在專案初期就與製造商溝通,詢問他們的最小走線寬度和間距要求。如果需要更多空間進行高速訊號佈線,請使用多層板。

提示:在完成佈局之前,請務必檢查您的設計規則。這有助於避免日後進行代價高昂的修改。

提前規劃並與製造商合作可以解決許多問題。這能確保高速訊號穩定,電路板可靠運作。

利用55法則優化PCB性能

版面和佈線技巧

透過巧妙的佈局和佈線,您可以提升PCB的效能。將元件放置在適當的位置有助於更快解決問題並節省成本。短走線有助於保持訊號強度並防止幹擾。走線之間足夠的間距可以防止訊號混疊和衰減。使用相同的走線寬度有助於控制阻抗並防止電壓降。如果優先佈線重要的訊號,您的設計將更有效率可靠。

將零件放置在合理的位置,以便於維修。

使用短訊號線可以保持訊號強度。

在導線之間留出間距,以防止訊號幹擾。

為了獲得良好的阻抗,請保持走線寬度相同。

首先路由關鍵訊號,以避免後續出現問題。

提示:使高速訊號路徑短而直接。

模擬與驗證

在製作PCB之前,請務必使用模擬工具檢查您的設計。許多工具都包含超過100條規則,例如55條規則,可協助您及早發現問題。快速仿真引擎讓您能夠快速檢查問題。您可以忽略誤報以節省時間,並專注於真正的問題。更強大的過濾功能可讓您建立清單來檢查重要訊號。區域裁切工具可協助您查看設計中的小部分,以便進行更深入的檢查。

獨特之處 | 簡介 |

|---|---|

預定義規則 | 超過 100 條規則,滿足不同的設計需求,其中包括 55 個規則。 |

高效嵌入式引擎 | 許多引擎都能快速自檢故障。 |

對虛假違規行為的管理 | 忽略誤報以節省時間。 |

增強的過濾能力 | 列出清單,以便檢查重要訊號。 |

面積作物功能 | 查看較小的設計區域以便更好地進行檢查。 |

注意:在製作 PCB 之前,請使用模擬工具檢查訊號路徑和間距。

與製造商合作

透過與製造商合作,您可以改進您的PCB設計。交錯式微孔比堆疊式微孔成本更低,並且能提高電路板的強度。填充空孔可防止水滲入,避免電路板損壞。在QFN散熱焊盤中使用更多微孔有助於焊錫流動,並防止加熱時出現問題。在邊緣留出空間可以確保切割時電路板的安全。

選擇交錯排列的微孔,可以增強電路板的強度。

填滿空孔以防止水進入。

為了獲得良好的焊接效果,在導熱焊盤上使用更多的微孔。

切割時,邊緣要留出空間,以保護砧板。

提示:儘早與製造商溝通,確保您的設計能夠支援強大的高速訊號。

在高速PCB設計中應用55法則,可以獲得更好的訊號完整性並減少錯誤。此法則有助於降低電磁幹擾和串擾,使電路運作更可靠。為了改進您的PCB設計,請嘗試以下方法:

使用 約束管理 幫助您規劃設計。

使用已經行之有效的設計可以節省時間並避免問題。

利用自動化技術準備生產所需的文件,提升產品品質。

不斷學習新知識,經常練習,才能每次都做出更好的PCB板。

常見問題

在PCB設計中,「55規則」是什麼意思?

使用55法則,確保每條訊號線與其他線路之間至少保持五倍於其寬度的距離。這有助於降低電路中的雜訊和乾擾。

55法則可以應用在所有PCB設計上嗎?

對於高速或敏感訊號,應使用 55 規則。對於低速或簡單的電路,可能不需要這麼大的間距。務必先檢查您的設計需求。

55 規則如何幫助解決 EMI 問題?

你降低 電磁干擾 (電磁幹擾)可以透過保持電路走線之間的足夠距離來降低。 55 規則使得訊號更難在走線間跳躍。這有助於保持電路的清潔和可靠。

如果你的PCB製造商無法滿足55規則怎麼辦?

你應該儘早與製造商溝通,詢問他們的最小走線寬度和間距要求。如果他們無法滿足 55 規則,你可能需要調整設計或使用更多圖層。