VLSI設計サイクルとは何かと疑問に思うかもしれません。このプロセスは、段階的に動作するチップを作るのに役立ちます。超大規模集積回路(VLSI)では、半導体技術を用います。これにより、1つのチップに何百万個ものトランジスタを集積することができます。サイクルの各段階は重要です。ステップを省略すると、エラーが発生したり、動作しないチップができたりする可能性があります。VLSI分野は急速に成長しており、世界市場は約 634.85年には2025億米ドル2034年までに1兆553億9000万米ドルに達する可能性があります。サイクルでは通常、以下の主要な段階を辿ります。

要件の収集

システムレベル設計

RTL設計

機能検証

合成

場所とルート

物理的検証

半導体技術は、私たちが毎日使用する電子機器に影響を与えています。

製品仕様

仕様策定フェーズは、VLSI設計サイクルの最初のステップです。ここでは、チップに何をさせるかを決定します。また、どの程度の動作を期待するかも決定します。このステップは、後で適切な選択を行うのに役立ちます。このステップを適切に実行すれば、チップは確実に正常に動作するでしょう。また、大きなミスを回避し、時間を節約することもできます。

要件

あなたが持っている必要があります 明確な要件 VLSIチップの設計を始める前に、これらの要件を策定する必要があります。これらの要件は、チップに何を実行させるべきかを示します。また、チップの速度、消費電力、サイズも規定します。チップに必要なすべての機能をリストアップします。これらの詳細を記述することで、全員が目標を把握しやすくなります。設計が人々のニーズに合致していることを保証できます。

ヒント:要件は簡単な言葉で書きましょう。短い文章を使い、難しい言葉は使わないようにしましょう。

多くのチームは要件を整理するために様々な方法を採用しています。以下に、一般的な方法をいくつか示します。

方法論 | 詳細説明 |

|---|---|

システムVerilog | チップの動作確認ツールを多数搭載。オブジェクト指向プログラミングとランダムテストを採用しています。 |

ユニバーサル検証方法論(UVM) | SystemVerilog を使用します。これにより、チームは再利用できるテストを構築できます。 |

VHDL | チップ設計の作成とチェックによく使用されます。ハードウェアのモデル化とテストに役立ちます。 |

e(スペックマン) | チップをチェックするための強力なツールを備えています。ルールに基づいたランダムテストを採用しています。 |

C/C++ と Python | テスト システムおよびテスト ベンチの作成に使用されます。 |

システムの目標

あなたが設定した システム目標 設計の指針となる目標を設定します。これらの目標には、チップの速度、コスト、消費電力などが含まれます。チップが他のデバイスとどのように連携するかを決定します。また、将来の変更についても計画します。目標を設定することで、チームが計画通りに作業を進めることができます。

仕様段階は、VLSI チップ設計において非常に重要です。 これはプロセス全体の基盤となります。優れた仕様は、チップが期待通りに動作することを保証します。これがプロジェクトの成功の鍵となります。

アーキテクチャ

システムデザイン

あなたは アーキテクチャフェーズ チップの動作を計画する段階です。チップの各部品が何をするかを決定します。また、これらの部品が互いにどのように通信するかも決定します。このステップは、大きな問題をより小さく、より簡単なタスクに分割するのに役立ちます。チップが何を実行しなければならないかを検討し、部品を最適に配置する方法を選択します。

いくつかの中から選ぶことができます 建築様式それぞれのスタイルには独自の長所があります。チップを一から作れるスタイルもあれば、時間を節約するために既製の部品を使うスタイルもあります。 一般的なスタイルを示す表を以下に示します。 そして何が彼らを特別なものにしているのか:

建築様式 | 詳細説明 |

|---|---|

フルカスタムデザイン | チップ全体をゼロから構築します。これにより、最高の速度と電力消費を実現できますが、多くの時間とスキルが必要です。 |

セミカスタムデザイン | 既製のパーツとカスタムパーツをいくつか使用します。これにより時間を節約でき、良好な結果が得られます。 |

プログラマブルロジックデバイス(PLD) | チップを作った後でも動作を変更できます。アイデアを素早くテストするのに最適です。 |

システムオンチップ (SoC) 設計 | 1つのチップに多くの部品を集積することで、チップは小型化され、高速化されます。スマートフォンやスマートデバイスに搭載されています。 |

既成設計 | すでにテスト済みですぐに使える部品を使用します。これは迅速で、多くの製品に適しています。 |

ヒント:プロジェクトのニーズに合ったアーキテクチャを選びましょう。速度、パワー、そして使える時間を考慮してください。

アーキテクチャの選択は、チップの消費電力と動作速度に影響します。特別なテクニックを使うことで、消費電力を節約し、速度を向上させることができます。その方法をいくつかご紹介します。

技術 | 詳細説明 |

|---|---|

低電力コンポーネントを使用する | 消費電力の少ない部品を選びましょう。チップがバッテリーで動作する場合、これは効果的です。 |

パワーゲーティング | 必要のないときはチップの一部をオフにします。 |

動的電圧および周波数スケーリング(DVFS) | チップの動作に応じて、チップの速度と電力使用量を変更します。 |

デューティサイクリング | 必要なときだけ回路をオンにします。 |

信号の切り替えを最小限に抑える | 信号の変化頻度を減らしてエネルギーを節約します。 |

負荷容量の最適化 | 出力の負荷を下げて消費電力を抑えます。 |

マルチスレッショルドCMOS(MTCMOS) | さまざまなタイプのスイッチを使用して、重要な領域の電力を節約します。 |

電力を考慮した合成 | チップを構築するときに、電力節約に重点を置くようにツールを設定します。 |

RTLでのクロックゲーティング | 使用されていない部分では時計を停止し、無駄なエネルギーを削減します。 |

ボディバイアス | 電圧を変更して漏れを減らし、電力を節約します。 |

階層的な電力ドメイン | チップをゾーンに分割して電力をより適切に制御します。 |

FinFETテクノロジーの活用 | リーク電流が少なく、低電力でも適切に動作する特殊なトランジスタを使用します。 |

ブロック図

チップの仕組みを示すブロック図を描きます。この図では、チップの各部分をシンプルな図形で表しています。これらの図形を線で繋ぐことで、データの流れを示します。分かりやすいブロック図は、チップの仕組みを誰もが理解するのに役立ちます。

ブロック図を作成するときは、次の点に注意してください。

チップの主要部分をすべて表示します。

データフローに明確な線を描きます。

各ブロックにその役割のラベルを付けます。

図はシンプルで読みやすいものにしてください。

明確なブロック図は、問題を早期に発見するのに役立ちます。また、チームメンバーがチップについて話し合い、製造開始前に変更を加えるのにも役立ちます。

RTL設計

RTL設計段階では、アイデアをチップの動作を記述するコードに変換します。VerilogやVHDLなどの言語を使用してコードを記述します。データの移動方法とチップの各部の動作に焦点を当てます。この段階は、チップの動作ルールを定めるため、非常に重要です。

RTLコーディング

RTL設計は、各ブロックの動作を示すコードを書くことから始めます。物理的なレイアウトについてはまだ気にする必要はありません。ロジックと信号の流れを記述します。チップが入力にどのように応答するかを示すために、シンプルなステートメントを使用します。各パーツが計画通りに連携して動作することを確認します。

ヒント:明確でシンプルなコードを書きましょう。難しい部分はコメントで説明しましょう。こうすることで、後であなたとチームが設計を理解しやすくなります。

RTL設計では様々な課題に直面します。以下に、最も一般的な課題をまとめた表を示します。

課題 | 詳細説明 |

|---|---|

設計の複雑さ | 大規模な設計を管理する必要があります。部品の数が増えると、ミスが発生しやすくなり、作業時間も長くなります。 |

設計の正確性を確保する | コードがチップに実行させたい動作と一致していることを確認する必要があります。 |

電力消費の管理 | チップを正常に動作させながらエネルギーを節約する方法を探します。 |

これらの課題には注意が必要です。注意しないと、エラーが発生したり、チップが過剰な電力を消費したりする可能性があります。

機能検証

RTLコーディングが完了したら、設計検証に移ります。コードが期待通りに動作するかテストします。テストベンチとシミュレーションツールを使用します。チップを組み立てる前に、RTL設計のあらゆる部分をチェックし、ミスがないか確認します。

チップが正しく応答するかどうかを確認するために、多くのテストを実行します。バグを発見したら、早期に修正します。設計検証は、後々コストのかかるエラーを回避するのに役立ちます。RTL設計が目標に合致していることに確信が持てるまで、このプロセスを繰り返します。

注: 適切な設計検証は時間とコストを節約します。問題が大きくなる前に発見できます。

RTL設計は信頼性の高いチップを開発する上で重要なステップであることを覚えておいてください。綿密なコーディングと強力な設計検証は、適切に動作し、ニーズを満たすチップの構築に役立ちます。

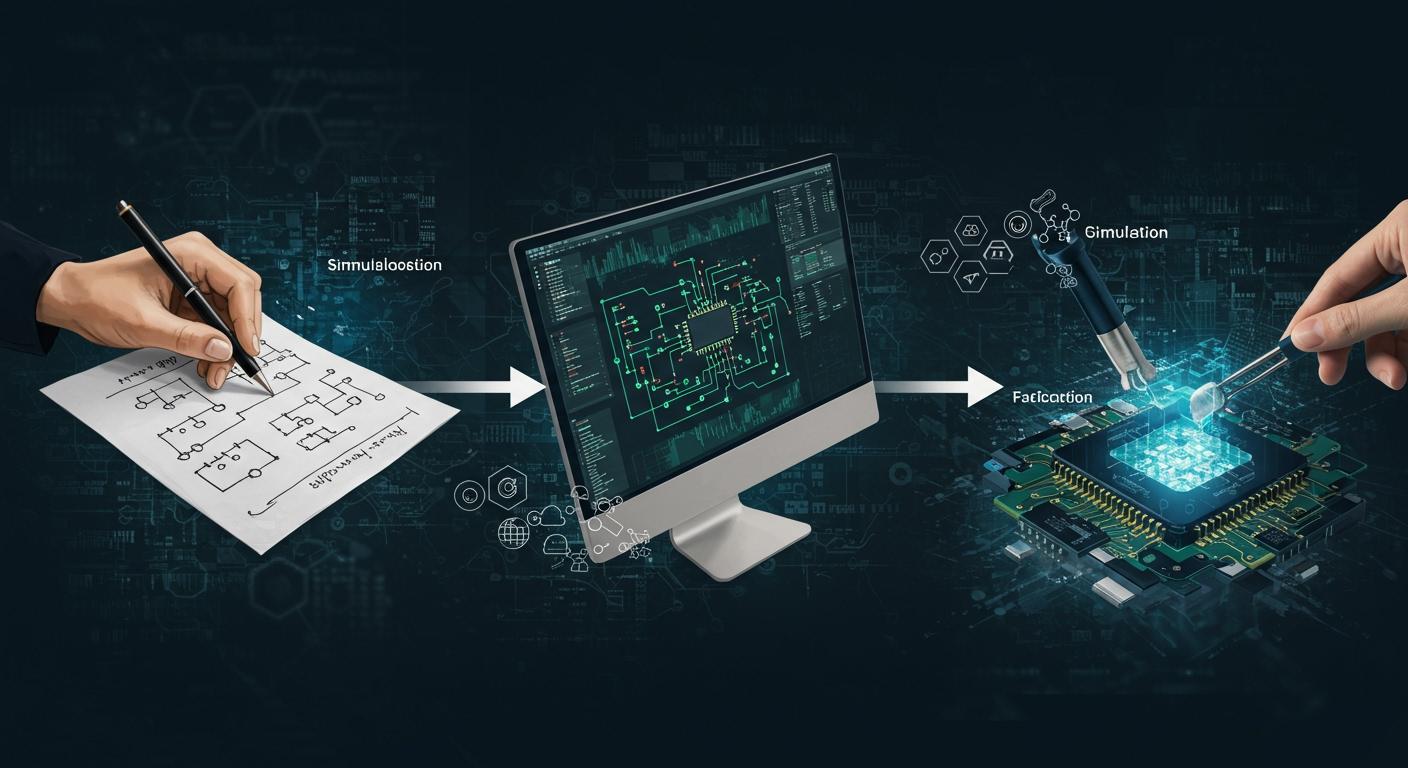

VLSI設計フローの概要

VLSI設計サイクルについて学び始めると、 VLSI設計フロー アイデアから実際に動作するチップに至るまでの明確な道筋を示します。このフローにより、ミスを回避し、チップ設計が計画通りに機能することを確認できます。

VLSI設計フローの段階

VLSI設計フローでは、一連のステップに従って作業を進めます。各ステップは前のステップに基づいて構築されます。フローにおける一般的な順序は以下のとおりです。

概念化と仕様

建築設計

ロジック設計

RTL合成

ネットリストとフロアプランニング

配置と配線

物理的検証

タイミング解析

抽出とシミュレーション

テープアウト

主要な活動

フローの各段階にはそれぞれ特別な役割があることに気づくでしょう。VLSI設計フローは明確な計画から始まり、実際のチップで終わります。各段階で作業内容をチェックすることで、問題を早期に発見し、問題が深刻化する前に修正することができます。 フローには、仕様、設計入力、合成、検証、レイアウト、製造などのステップが含まれます。 一つ一つがチップ設計の正確性を保証するのに役立ちます。この慎重なサイクルにより、エラーを最小限に抑え、高い品質を維持できます。

フローはあらゆるVLSIプロジェクトの指針となることがお分かりいただけるでしょう。フローに従うことで、チップ設計は堅牢で信頼性の高いものになります。フローは、あらゆる成功するVLSIチップの基盤です。

論理合成

RTLからゲートへ

論理合成は、アイデアを実際のハードウェアへと変換するための重要なステップです。この段階では、RTLコードを論理ゲートに変換します。この作業には専用のツールを使用します。これらのツールはRTLコードを読み取り、チップ上に構築可能なゲートネットワークを作成します。

ロジック合成には主に 3 つのステップがあります。

翻訳:このツールは、RTLコードをブール方程式を使用する形式に変換します。このステップはチップテクノロジーに依存しません。

最適化:このツールはブール方程式を簡素化します。そのために、積和などの手法が用いられます。

テクノロジーマッピング:このツールは、最適化された方程式をライブラリ内の実際のゲートとマッチングさせます。設計ニーズに適したゲートを選択します。

ヒント: 合成を始める前に、必ずRTLコードにエラーがないか確認してください。クリーンなコードほど、より良い結果が得られます。

最適化

最適化は、ニーズに最適なチップを実現するのに役立ちます。チップは小型で高速、そして消費電力が少ないことが求められます。論理合成ツールは、プロセス中に適切な選択を行うことで、これらの目標達成を支援します。

最適化がチップにどのような影響を与えるかを示す表を以下に示します。

側面 | VLSIチップへの影響 |

|---|---|

エリア最適化 | 物理的なフットプリントを削減し、ウェーハ上にチップを多く配置できるため、歩留まりが向上し、コストが削減されます。 |

速度最適化 | ネットワークが高速化すると、多くの場合、消費領域が大きくなるため、速度と領域の間でトレードオフが必要になります。 |

エネルギー消費 | ゲートが大きいほど静電容量が増加し、スイッチング時のエネルギー消費量が増加します。 |

面積、速度、そして消費電力のバランスを取る必要があります。チップを高速化すると、サイズが大きくなり、消費電力も増加する可能性があります。一方、チップを小型化すると、動作速度が低下する可能性があります。優れたロジック合成は、最適なバランスを見つけるのに役立ちます。

面積最適化により、ウェハ上により多くのチップを搭載できます。これによりコストが削減され、より多くの機能を追加できるようになります。

速度の最適化によりチップの動作は速くなりますが、より多くのスペースとエネルギーを使用する可能性があります。

パフォーマンスを損なうことなく新しい機能を追加するには、スペースを効率的に使用することが重要です。

あらゆるVLSIプロジェクトで論理合成が用いられます。論理合成は設計を形作り、実環境で適切に動作するチップの構築に役立ちます。

物理設計

その 物理設計段階 チップのロジックを実際のレイアウトに変換する段階です。チップの各部品をどこに配置し、どのように配線で接続するかを決定します。このステップは、VLSIの物理設計において非常に重要です。チップの動作がどれだけ良好で、問題なく製造できるかどうかを左右するからです。

フロアプランニング

物理設計段階はフロアプランニングから始まります。ここでは、チップをブロックに分割し、各ブロックに専用のスペースを割り当てます。各ブロックのサイズと配置場所を検討します。適切なフロアプランニングは、回路が密集するエリアを回避し、信号を高速に伝送するのに役立ちます。また、電源ラインとクロックラインのスペースも計画します。このステップは、VLSIの物理設計プロセスの残りの構造を決定します。

この段階では、フロアプランニングやその他のタスクに役立つツールが多数あります。 最も人気のあるツールには次のようなものがあります:

Synopsys IC Compiler II: 高速な配置配線、電力を考慮した設計。

Mentor Graphics Calibre: ルールをチェックし、レイアウトを回路図に一致させます。

ANSYS RedHawk: パワーと信頼性をチェックします。

Tanner ツール: アナログおよびミックス信号レイアウトに適しています。

Avanti Hercules: 信号と電力の整合性をチェックします。

OpenROAD: 物理設計用のオープンソース ツール。

KLATencor L-Edit: カスタム IC レイアウトに使用されます。

ヒント: プロジェクトのニーズとチームのスキルに合ったツールを選択してください。

配置と配線

フロアプランニングの後は、配置配線に移ります。各セルまたはブロックを所定の位置に配置し、関連するブロック同士を近づけます。これにより、信号伝達が高速化し、消費電力も削減されます。また、チップが過熱しないように注意する必要があります。

次に、配線を行います。ブロック間の信号経路を描き、速度のバランスを取り、経路の混雑を避けます。また、レイアウトがチップ製造のルールに従っているかどうかも確認します。これらの手順は、チップの動作をスムーズにし、製造を容易にするのに役立ちます。

物理設計段階では、次の主な手順に従います。

チップをパーティション分割してフロアプランします。

セルとブロックを配置します。

クロックツリーを構築します。

配線を配線します。

ルールと製造可能性を確認します。

電力を最適化します。

物理設計段階が完了すると、製造のためのレイアウトが完成します。このステップは すべてのVLSIプロジェクトの鍵.

テスト容易性を考慮した設計

VLSI チップを扱うときは、簡単にテストできることを確認する必要があります。 テスト容易性を考慮した設計は、問題を早期に発見するのに役立ちます チップが顧客に届く前に、問題箇所を修正します。チップに特別な機能を追加することで、すべてが計画通りに動作するかを確認できます。これらの機能により、テストが迅速化され、製造コストの削減につながります。

テスト機能

チップのテスト容易性を向上させるために、いくつかの手法が用いられます。これらの手法は、欠陥を検出し、チップが正常に動作することを保証するのに役立ちます。

スキャン設計により、テスト中にチップ内のフリップフロップを制御およびチェックできます。

境界スキャンを使用すると、プローブを使用せずにボード上のチップ間の接続をテストできます。

組み込みセルフテスト (BIST) は、チップ内にテスト ハードウェアを追加して、チップ自体をテストできるようにします。

メモリ BIST (MBIST) は、チップ内のメモリ ブロックをチェックします。

ATPG (自動テストパターン生成) は、製造後に障害を見つけるのに役立つパターンを作成します。

これらの機能により、テスト範囲が拡大し、テストに必要な時間が短縮されます。不具合を迅速に発見し、不良チップを顧客に送ることを回避できます。

ヒント: 早期にテスト機能を追加する 設計プロセスで。これによりテストが容易になり、コストも削減されます。

これらの手法を用いることで、多くのメリットが得られます。以下の表は、テスト容易化設計がチップにどのような効果をもたらすかを示しています。

商品説明 | 詳細説明 |

|---|---|

障害検出 | |

製造歩留まり向上 | 生産中に問題を修正し、より良質なチップを入手します。 |

信頼性の向上 | チップが長期間にわたって正常に動作することを保証します。 |

複雑なチップをより迅速かつ正確にテストできます。期待通りに動作する高品質なチップを提供できます。

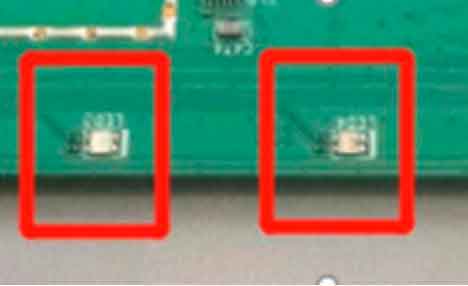

スキャンチェーン

スキャンチェーンはVLSIチップのテストにおいて重要な役割を果たします。フリップフロップをチェーン状に接続することで、テスト中に値を設定したり読み取ったりすることができます。この構成により、チップを分解することなく内部をチェックできます。

スキャンチェーンは、ロジックブロックの故障を検出するために使用します。各フリップフロップを制御し、チップ内の信号の流れを観察できます。この手法は、通常のテストでは見逃されがちな問題を発見するのに役立ちます。

スキャンチェーンを追加することで、チップのテストが容易になり、信頼性が向上します。また、チップが製品に組み込まれた後に発生する、コストのかかる故障のリスクも軽減されます。

注: スキャン チェーンを適切に計画すると、時間を節約し、チップの品質を向上させることができます。

テスト容易性設計を早期に統合することでテスト時間を短縮できます 高額な損失につながるミスを回避し、より長く使い続け、より優れた性能を発揮するチップを開発できます。

タイミング解析

タイミング解析は、チップが適切な速度で動作していることを確認するのに役立ちます。このステップでは、チップ内の信号が十分な速度で伝送されているかどうかを確認します。タイミング解析を省略すると、チップが計画通りに動作しない可能性があります。VLSIにおいて、タイミング解析は設計完了前に行う最も重要なチェック項目の一つです。

静的タイミング

あなたが使う 静的タイミング解析 (STA) テストパターンを実行せずにチップのタイミングをチェックできます。STAは回路内のすべてのパスを監視し、信号が時間通りに到着するかどうかを確認します。この手法は、問題を早期に発見するのに役立ちます。入力ベクトルを使用する必要がないため、すべての可能性のあるパスを迅速にチェックできます。

ここでいくつか紹介します 一般的なタイミング解析方法 次のようなものを使用できます。

静的タイミング解析(STA)

動的タイミング解析(DTA)

統計的静的タイミング解析(SSTA)

サインオフタイミング分析

マルチコーナー・マルチモード(MCMM)解析

オンチップ変動(OCV)解析

STAはタイミング違反を防ぐ上で重要な役割を果たします。信号はフリップフロップやレジスタに適切なタイミングで到達する必要があります。信号の到達が遅すぎたり早すぎたりすると、チップが故障する可能性があります。 設計上の欠陥の80%以上 シリコン上の欠陥はタイミング違反によって発生します。STAは、このようなコストのかかるミスを回避するのに役立ちます。

注:静的タイミング解析では、チップの最大速度をチェックし、すべての信号が時間どおりに到着することを確認します。このステップは、チップの動作に不可欠です。

タイミングクロージャ

タイミングクロージャとは、チップ内のすべてのタイミング問題を修正するプロセスです。すべての信号がタイミング目標を達成することが求められます。設計の変更、ブロックの移動、配線長の調整などが必要になる場合があります。タイミングクロージャには多大な労力がかかりますが、チップを正常に動作させる鍵となります。

タイミングクロージャに到達するには、次の手順に従います。

STA からのタイミング レポートを分析します。

タイミングに失敗したパスを見つけます。

これらのパスを修正するには設計を変更します。

STA を再度実行して、問題が解決したかどうかを確認します。

タイミングが完了するまで繰り返します。

タイミングクロージャを支援する特別なツールを使うこともできます。これらのツールは、どのパスに修正が必要かを示します。設計を変更して結果をすぐに確認できます。タイミングクロージャにより、チップが希望する速度で動作することが保証されます。

ヒント: タイミングの調整は早めに始めましょう。 タイミングの問題 最後には非常に困難になる可能性があります。

VLSI設計を完成させる前に、タイミングクロージャが必要です。このステップにより、チップが実際に動作するという確信が得られます。

物理的検証

物理的な検証チェック チップのレイアウトが製造準備が整っているかどうかを確認します。チップが適切に動作し、ファウンドリのルールをすべて遵守していることを確認する必要があります。このステップは、チップ製造前にミスを見つけるのに役立ちます。様々なチェックを行い、レイアウトが安全かつ正しいことを確認します。

物理的な検証の主な手順をまとめた表がこちらです。 そして彼らは何をするのか:

検証ステップ | 目的 |

|---|---|

デザインルールチェック(DRC) | レイアウトが 鋳造所の幅に関する規則 と間隔。 |

レイアウトと回路図(LVS) | レイアウトが回路図または回路図と一致していることを確認します。 |

電気ルールチェック(ERC) | 配線の欠落や静電容量の過剰などの電気的な問題を検出します。 |

DRC

まず、DRC(デザインルールチェック)と呼ばれる設計ルールチェックを行います。このチェックでは、チップのレイアウトをファウンドリのルールと比較します。これらのルールは、配線の幅と間隔を規定しています。これらのルールに違反すると、チップが動作しないか、製造が困難になる可能性があります。

DRCは物理検証の一部である配線が近すぎる、形状が小さすぎるといった問題を見つけるのに役立ちます。これらの問題を修正することで、チップの構築が容易になり、信頼性が向上します。

プロセス | フォーカス | 目的 |

|---|---|---|

DRC | 物理的検証 | 設計ルールに従ってチップを製造できることを確認します。 |

ヒント:レイアウトを完成させる前に必ずDRCを実行してください。このステップは時間とコストを節約します。

LVS

DRCの後は、レイアウトと回路図(LVS)の検証を行います。この検証では、レイアウトが回路図と一致していることを確認します。レイアウト内のすべての配線と部品が回路図と一致するようにする必要があります。

LVSは電気的な検証です。チップが計画通りに動作するかどうかを確認します。LVSで問題が見つかった場合は、次のステップに進む前に修正する必要があります。

プロセス | フォーカス | 目的 |

|---|---|---|

LVS | 電気検証 | 正しく作業するために、レイアウトが回路図と一致していることを確認します。 |

物理検証はVLSIプロセスの重要な部分です。DRCとLVSを使用することで、設計が正しく、次のステップに進む準備ができていることを確認できます。

加工

VLSI設計サイクルのテープアウトが完了したら、 製造このステップで、チップ設計が現実のものとなります。あなたのアイデアはシリコンチップへと形を変え、携帯電話、コンピューター、その他のデバイスに組み込まれます。

ウェハ処理

ウエハー処理 チップ製造の最初の工程です。ウエハーと呼ばれる薄いシリコン片を使います。その上に層や回路を形成するために、多くの工程を経ます。それぞれの工程がチップに重要な機能を追加します。

表面クリーニング

ほこりを取り除くためにウェハーを洗浄します。初期酸化

ウェーハ上に薄い酸化物層を成長させます。CVD堆積

特殊なガスを使ってウェハー上に新しい材料を置きます。コーティングフォトレジスト

光に反応する材料でウェハーを覆います。メタライゼーションと相互接続

チップの各部分を接続するために金属を追加します。化学機械研磨(CMP)

ウエハーを研磨して平らで滑らかにします。最終テストとパッケージング

チップをテストし、パッケージ化する準備をします。

複雑なチップを作るには、いくつかのステップを繰り返す必要があるかもしれません。各段階は、計画に合ったチップを作るのに役立ちます。

ヒント: ウェハー処理を慎重に行うことで欠陥を防ぎ、より優れたチップを製造することができます。

鋳造所の階段

ウェハ処理後、チップはファウンドリーに送られ、テープアウトされます。ファウンドリーはそれぞれ独自の方法でチップを製造しており、ビジネススタイル、技術、研究目標も異なります。

メーカー | ビジネスモデル | プロセスノードフォーカス | 研究開発の焦点 |

|---|---|---|---|

TSMC | 純粋なファウンドリ | より小さなプロセスノード | プロセスノードの改善と歩留まりの向上 |

インテル | 垂直統合 | 技術リーダーの復帰 | 新しいパッケージ、AIチップ、量子コンピューティング |

サムスン | ファウンドリーとメモリチップ | 高度なノード | メモリとロジックチップの新しいアイデア |

ニーズに合ったファウンドリーをお選びください。ファウンドリーによっては、より小型で高速なチップを製造するものもあれば、新しいパッケージや特殊な機能に取り組むものもあります。テープアウトの工程は、ファウンドリーの得意分野によって異なります。

製造はVLSI設計サイクルにおいて非常に重要な部分です。テープアウト後に良質なチップを得るには、すべてのステップを踏む必要があります。

テストとパッケージング

電気試験

工場出荷前にすべてのチップを検査する必要があります。電気テストは、チップが計画通りに動作することを確認するためのものです。このステップは、チップの製造時に発生した問題を発見するのに役立ちます。チップのテストには様々な方法があります。一般的な方法は以下の通りです。

断層モデル化

自動テストパターン生成(ATPG)

境界スキャンテスト(JTAG)

機能テスト

パラメトリックテスト

DFTを使用すると、チップの設計時に特別な機能を追加できます。これらの機能により、テストが簡素化されます。BIST(Built-In Self-Test)を使用すると、チップ自体をテストできます。そのため、追加のツールは必要ありません。ATPGは、迅速に障害を発見するためのテストパターンを作成します。これらの手法は、コストと時間の節約に役立ちます。お客様がチップを受け取る前に問題を修正できます。適切なテストは、正常に動作するチップだけがユーザーに提供されることを意味します。これにより、ユーザーの満足度が向上します。

ヒント:電気テストは欠陥を早期に発見するのに役立ちます。VLSIチップが正常に動作するかどうかを確認できます。

梱包方法

テスト後、チップを保護し、接続する必要があります。この作業はパッケージングによって自動的に行われます。チップのパッケージング方法は、チップの動作性能に影響を与えます。また、寿命にも影響します。熱、電力、信号について考慮する必要があります。

パッケージングにおいては相互接続技術が重要です。 マイクロバンプシリコン貫通ビア(TSV)、再配線層(RDL)はチップ間の接続に役立ちます。マイクロバンプはチップと基板間の接続に適していますが、熱や振動の問題が発生する場合があります。エレクトロマイグレーション(EM)とサーマルマイグレーション(THM)は信頼性を損なう可能性があります。

TSVはチップ内で信号と熱を上下に移動させます。これによりチップの動作が向上します。しかし、チップが高温または低温になると、異なる材料ではひび割れや破損が生じる可能性があります。

パッケージングを改善するには、熱、電気、そして力を研究する必要があります。高密度配線や高度な熱伝導材といった新素材の使用は、熱制御に役立ちます。また、チップの寿命も長くなります。チップの高速化と小型化が進むにつれて、優れたパッケージ設計の重要性はますます高まっています。

あなたはそれを見ることができます テストとパッケージング どちらも重要です。チップがうまく機能し、長持ちするのに役立ちます。

シリコン検証

チップの製造が完了したら、設計通りに動作するか確認する必要があります。このステップはシリコン検証と呼ばれます。チップが元の設計と一致し、実際に問題なく動作することを確認する必要があります。

製造後のチェック

製造後、工場から出荷された最初のチップをテストします。これらのチップはプロトタイプと呼ばれます。専用の基板に実装し、多くのテストを実行します。以前のチェックでは検出されなかった問題を探します。最初のテストではバグが見つからない場合もありますが、チップが実際のシステム速度で動作することで、それらのバグも発見できます。

シリコン検証には標準的なプロセスに従います。

プレシリコン検証 チップを製造する前に、ソフトウェアを使ってチップをテストします。シミュレータでテストケースを実行します。このステップでは、RTLコードが仕様と一致しているかどうかを確認します。

ポストシリコン検証は、実際のチップを入手した後に始まります。チップをハードウェア上でテストし、実際の条件下でリアルタイムに動作を確認します。

注: ポストシリコン検証は、チップがフルスピードで動作しているときや実際の環境でのみ発生する問題を見つけるのに役立ちます。

最終成果物

すべてのチェックが完了すると、チップが市場に投入できる状態かどうかが分かります。チップの性能、消費電力、そしてすべての目標を満たしているかどうかを検証します。問題が見つかった場合は、次のチップを製造する前に修正することができます。

以下は、シリコン前段階とシリコン後段階の違いを示す簡単な表です。

手順 | それが起こったとき | テスト対象 | テストのスピード |

|---|---|---|---|

プレシリコン検証 | 製造前 | ソフトウェアシミュレータ | 実際のシステム速度ではない |

シリコン後検証 | 製作後 | 本物のハードウェア | 実際のシステム速度 |

VLSIチップが計画通りに動作することを確認するには、シリコン検証が必要です。このステップにより、設計が現実世界で成功するという確信が得られます。

VLSIチップ設計の各段階を踏むことで、より信頼性の高い設計が可能になります。これにより、ミスを回避し、作業を安定させることができます。 VLSI設計フローを理解する 速度、サイズ、電力消費の改善に役立ちます。新しい機能としては、 AI駆動型自動化と3D統合 VLSIの未来を変えています。仕事で成長したいなら、 新しいスキルを学び、資格を取得する専門家に相談しましょう。このサイクルは、より優れたチップを開発し、テクノロジーの先頭に立つために役立ちます。

トレンド | 半導体技術への影響 |

|---|---|

AI駆動型設計自動化 | チップ設計をより速く簡単に |

電力最適化戦略 | 小型デバイスの動作を向上 |

3D統合技術 | 速度と熱の制御が向上します |

セキュリティ第一のアプローチ | ハッカーからチップを守る |

高度なシミュレーションツール | より速く、より正確に設計をチェック |

自分が知っていることを確認し、弱点を修正します。

特別授業を受ける。

現場の人々と会って話をしましょう。

FAQ

VLSI 設計サイクルとは何ですか?

VLSI設計サイクルに従って、段階的にチップを作成します。このサイクルは、チップの計画、構築、テストに役立ちます。各段階で、チップが適切に動作し、ニーズを満たしていることを確認します。

なぜ VLSI はエレクトロニクスにおいて重要なのでしょうか?

VLSIは、何百万もの小さな部品を1つのチップに収めるために使われます。これにより、デバイスはより小型、高速、そしてスマートになります。携帯電話、コンピューター、そして自動車はすべて、より優れた動作を実現するためにVLSIチップを使用しています。

デザインプロジェクトはどのように始めますか?

まず、チップに何をさせたいかを書き出します。明確な目標を設定し、機能をリストアップします。これにより、あなたとチームは集中力を維持し、ミスを防ぐことができます。

VLSI 設計に役立つツールは何ですか?

あなたが使う 描画用の専用ソフトウェアチップの設計、テスト、そしてチェック。Synopsys、Mentor Graphics、Cadenceなどのツールは、チップの製造前に設計、シミュレーション、検証を行うのに役立ちます。

チップを作った後に間違いを修正できますか?

テスト中にいくつかの間違いを発見し、修正することができます。大きな問題が見つかった場合は、設計を変更して新しいチップを作成する必要があるかもしれません。 綿密な計画は コストのかかるエラーを回避します。