はじめに

1.1 5G革命とPCBの課題

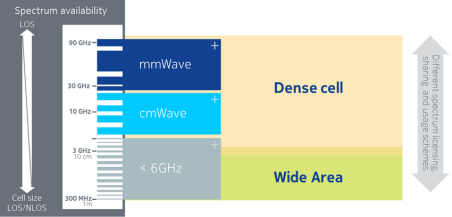

5G無線技術の世界的な展開は、4G LTEの登場以来、通信インフラにおける最も重要な変革を表しています。5Gは、広いカバレッジを実現する6GHz以下の周波数帯と、超高速通信を実現する24GHzから77GHzのミリ波(mmWave)周波数帯という2つの異なる周波数帯で動作します。

5Gネットワークの高速データ伝送には、プリント基板(PCB)設計においてかつてないほどの高精度が求められます。従来のPCBアプリケーションとは異なり、5Gシステムは信号周波数を扱う必要があり、微細な設計欠陥でさえも壊滅的な性能低下を引き起こす可能性があります。

業界分析によると、世界の5Gインフラ市場は2027年までに47.7億ドルを超えると予測されており、高性能PCBソリューションへの需要が急増しています。この成長は、材料特性、層構成、無線周波数における信号挙動の複雑な関係を熟知しなければならないPCB設計者にとって、機会と課題の両方を生み出します。4Gから5Gへの移行は、単なる段階的なアップグレードではなく、PCBスタックアップアーキテクチャの根本的な見直しを必要とします。

図1 – サブ6GHz帯とミリ波帯を強調した周波数スペクトル

1.2 5Gパフォーマンスにおけるスタックアップ設計の重要な役割

PCBスタックアップは、銅層、誘電体、コア基板を綿密に組み合わせた構造で、5Gの信号品質を支える基盤となります。ミリ波帯では、電磁エネルギーは、低周波アプリケーションに慣れた設計者にとって直感に反すると思われるような原理に従って動作します。信号波長はミリメートル単位にまで縮小されるため、

1 GHz では重要ではなかったビア スタブやトレースの不連続などの特徴は、28 GHz では信号反射と損失の主な原因になります。

適切に設計された5G PCBスタックアップは、複数の相反する要件を同時に満たす必要があります。信号反射を防ぐためのインピーダンス制御、信号強度を維持するための低挿入損失、回路間のクロストークを防ぐための効果的な電磁干渉(EMI)シールド、そして消費電力の大きいRFアンプからの熱を放散するための堅牢な熱管理です。スタックアップ構成はこれらの各パラメータに直接影響を与えるため、5G PCB設計プロセス全体の中で最も重要な決定事項となります。

2. 5G PCB要件の理解

2.1 5G周波数スペクトルと信号特性

サブ6GHz帯:広範囲のカバレッジの基盤

600MHzから6GHzまでの周波数帯を含むサブ6GHz帯は、5Gのカバレッジ・バックボーンを構成します。これらの低周波数帯域は、広域ネットワークの展開に必要な伝搬特性を備えており、ミリ波に比べて建物への浸透性と到達距離が優れています。PCB設計の観点から見ると、サブ6GHz帯の信号は、4G LTEよりも要求が厳しいものの、ミリ波アプリケーションほど過酷ではないという、中程度の課題を提示します。

mmWave帯域(24~77GHz):極めて高い精度が求められる ミリ波5Gは、主に24GHz、28GHz、39GHz、77GHz帯で動作し、PCB技術を限界まで押し上げます。28GHzでは、一般的なRogers RO4350Bラミネート(Dk = 3.48)の波長はわずか5.7mmです。これは、臨界共振長における1/4波長スタブの広がりがわずか1.4mmであることを意味します。従来のめっきスルーホールビアは、通常2~3mmのスタブを残しますが、大きな寄生共振器となり、信号整合性を完全に損なう可能性があります。

図2 – 物理的な寸法を示す詳細な波長比較

2.2 5Gスタックアップの主要な電気パラメータ

5G PCBの性能は複数の電気的パラメータによって左右され、スタックアップ設計においてはそれぞれを慎重に検討する必要があります。誘電率(Dkまたはεr)は信号伝搬速度と制御インピーダンス値を決定します。5Gアプリケーションでは、周波数と温度の両方におけるDkの安定性が最も重要です。温度によってDkが5%変化する材料は、インピーダンスの変動を引き起こし、反射を生じさせ、高精度RF回路における信号整合性を低下させます。

誘電正接(Df)は誘電損失を定量化するもので、損失正接(tan δ)とも呼ばれます。標準的なFR-4のDf値は10GHzで0.015~0.020ですが、Rogers RO3003などの高性能材料では、同じ周波数で0.0010と、15~20倍の改善が見られます。

5Gアプリケーションでは、インピーダンス制御の許容範囲が大幅に狭くなります。多くのアプリケーションでは±10%のインピーダンス許容範囲で十分かもしれませんが、5G RF回路では通常、±5%以上の厳密な制御が求められます。

| 材料 | 誘電 定数(Dk) | 誘電正接 (Df) | 最適なアプリケーション |

| FR-4規格 | 4.2~4.5 @ 1GHz | 0.015-0.020 | デジタル、サブ6GHz非クリティカル |

| ロジャース RO4350B | 3.48 @ 10GHz | 0.0037 | サブ6GHz RF、コスト効率の高いmmWave |

| ロジャーズRO3003 | 3.00 @ 10GHz | 0.0010 | 高性能ミリ波基地局 |

| RT / duroid 5880 | 2.20 @ 10GHz | 0.0009 | 超低損失 >20 GHz、フェーズドアレイ |

表1: 5G PCBアプリケーション向け高周波ラミネート材料の比較

2.3 物理的および熱的要件

5G PCBは、最新のRFトランシーバー、ベースバンドプロセッサ、電源管理回路、および関連するデジタルインターフェースの高密度配線要件に対応するために、通常10~16層の銅箔層を必要とします。直径0.1mmという極小のマイクロビア、ブラインドビアとベリードビア、そして任意の層への配線を特徴とする高密度相互接続(HDI)技術は、制御されたインピーダンス信号パスを維持しながら、5Gシステム統合に求められるコンポーネント密度を実現するために不可欠となります。

5G設計において、熱管理は大きな課題となります。基地局アプリケーションのパワーアンプは50~100ワットの電力を消費するため、動作中に85~100℃に達する局所的なホットスポットが発生します。PCB基板は、この熱を基板全体に拡散させ、ヒートシンクまたは熱管理システムに伝達するために、十分な熱伝導率(1.5 W/m·K以上)を備えている必要があります。相対温度指数(RTI)で測定される150℃以上の耐熱性は、持続的な動作条件下での材料の安定性を確保します。

5G PCBの製造公差は大幅に厳しくなっています。銅層間の位置合わせ精度は、従来の設計では±150μmでしたが、ミリ波アプリケーションでは±75μm(±3ミル)以上にする必要があります。

3. 5Gスタックアップの材料選択

3.1 高周波積層材料

ロジャースマテリアルズ:RFパフォーマンスの業界標準

ロジャース・コーポレーションの高周波ラミネートは、5G PCBアプリケーションの事実上の標準となっており、幅広い周波数範囲と温度範囲にわたって安定した誘電特性を綿密に設計しています。RO4000シリーズ、特にRO4350Bは、RF性能と製造性の優れたバランスを実現しています。10GHzにおける誘電率3.48±0.05、誘電正接0.0037のRO4350Bは、標準的なFR-4処理技術を使用しながら、特別なビア処理やドリル加工パラメータの変更を必要とせず、予測可能なインピーダンス制御を実現します。

より低損失が求められるアプリケーションには、RO3000シリーズが卓越した性能を提供します。セラミック充填PTFE構造のRO3003は、誘電率(Df)0.0010、誘電率(Dk)3.00という優れた特性を実現し、10MHzから40GHzまで極めて安定した特性を維持します。この材料は、基地局のパワーアンプ設計や、挿入損失の10分の1dBがシステム性能に影響を与えるその他のアプリケーションに最適です。ただし、その代償として、材料コスト(通常RO4350Bの3~5倍)が高く、製造要件もより厳しくなります。

図3 – ロジャースRO4350B積層構造の断面図(銅箔、樹脂システム、ガラス強化材を示す)

3.2 5GアプリケーションにおけるFR-4:限界を理解する

標準的なFR-4は、5G設計の特定の部分、特にデジタル信号処理部、電力分配ネットワーク、およびRF性能要件がそれほど厳しくない6GHz未満のアプリケーションでは依然として有効です。Shengyi、Panasonic、ITEQなどのメーカーが提供する最新の高品質FR-4は、適切な樹脂システムとガラス補強材を使用することで、5GHzで0.012~0.015のDf値を達成できます。

多くの 6 GHz 未満の信号パスで許容されます。

しかし、FR-4の限界は高周波数域で顕著になります。この材料の誘電率は、動作温度範囲(-40℃~+85℃)全体で±10%変動しますが、高周波ラミネートでは±2%です。この変動はインピーダンスの変動につながり、高速デジタルインターフェースで反射によるビットエラーを引き起こし、RFシステムのパフォーマンスを低下させる可能性があります。さらに、FR-4はガラス繊維で強化されているため、実効誘電率に局所的なばらつき(ファイバーウィーブ効果)が生じ、ガラス繊維パターンに対して斜めに配線されている場合に問題となります。

3.3 ハイブリッドスタックアップ戦略:パフォーマンスとコストの最適化

高周波ラミネートとFR-4を組み合わせたハイブリッドスタックアップは、複雑な5G設計において性能とコストのバランスをとる優れたアプローチを提供します。このコア戦略では、高価な低損失材料をRF信号が伝わる部分にのみ配置し、デジタル信号、電力分配、および機械的支持を担う内層には経済的なFR-4を使用します。典型的なハイブリッドスタックアップでは、RFマイクロストリップ伝送線路が配置される外側の2層(12層設計ではL1とL12)にRogers RO4350Bを使用し、内層をFR-4コアで構成します。

図4 – RF信号用のRogers RO4350B外層を示す12層ハイブリッドスタックアップの断面図

4. 5Gのレイヤー構成戦略

4.1 スタックアップの基本原則

具体的な層構成に入る前に、5G向けPCBスタックアップ設計にはいくつかの基本原則が存在します。製造において最も重要な考慮事項は対称性です。積層や熱サイクル中の反りを防ぐため、スタックアップは基板の中心線を中心にバランスをとる必要があります。これは、中心プレーンの反対側の銅箔重量、コア厚、プリプレグ数を一致させることを意味します。片面に銅箔が多い基板は、リフローはんだ付け後にポテトチップスのように反り返り、精密RFアセンブリには許容できない結果となります。

基準プレーンの隣接性も同様に重要です。すべての信号層は、途切れることのないグラウンドプレーンまたは電源プレーンを隣接して持つ必要があります。これにより、高周波信号に必要な低インダクタンスのリターンパスが確保されると同時に、信号層を干渉から保護することができます。

レイヤーペアリングとは、信号層を機能と電気的要件に基づいてグループ化することです。高速差動ペアは同一層に配線し、層をまたいでペアを分割するのではなく、蛇行配線によって長さを揃える必要があります。RF信号層は通常、マイクロストリップ伝送線路として実装できる外層に配置され、チューニングやデバッグが容易になります。

4.2 8層スタックアップ:5G設計のエントリーポイント

8層スタックアップは、IoTデバイス、スモールセル無線、またはシンプルなサブ6GHz RFモジュールといった基本的な5Gアプリケーションにおいて、実用的な最小層数です。より高層数のものと比較すると制限はあるものの、適切に設計された8層構造は、慎重な配線規則と部品配置により、中程度に複雑な設計を効果的にサポートできます。

推奨される8層構成:

∙ レイヤー1: RF信号と重要な高速(マイクロストリップ、50Ω)

∙ レイヤー2: グランドプレーン(プライマリRFリターンパス)

∙ レイヤー3: 高速デジタル信号(ストリップライン、50Ωまたは100Ω差動) ∙ レイヤー4: 電源プレーン(+3.3V、+1.8V分割)

∙ レイヤー 5: 電源プレーン (ミラーリング: +3.3V、+1.8V 分割)

∙ レイヤー6: 高速デジタル信号(ストリップライン、L3に直交)

∙ レイヤー7: グランドプレーン(二次リターンパス)

∙ レイヤー8: RF信号と重要な高速(マイクロストリップ、50Ω)

この構成は対称性(L1-L2-L3-L4がL8-L7-L6-L5をミラーリング)を実現し、すべての信号層に隣接するリファレンスプレーンを確保し、電源プレーンを中央に配置することで、その容量がデカップリングに最も効果的になるようにします。一般的な誘電体の厚さは、L1-L2 = 6ミル(RF用RO4350B)、L2-L3 = 8ミル(コア)、L3-L4 = 14ミル(プリプレグ)、L4-L5 = 20ミル(コア)で、L8に対して対称的にミラーリングされます。

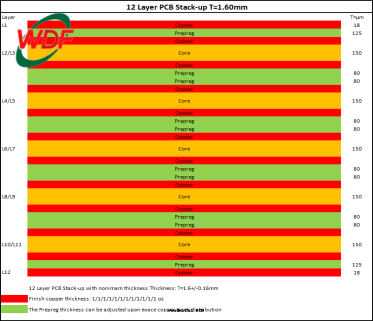

4.3 12層スタックアップ:高度な5Gアプリケーション

高度な5Gシステム基地局モジュール、大規模MIMOアンテナアレイ、またはハイエンドスマートフォンでは、12層スタックアップが最適な結果を得るために必要な配線密度と信号整合性性能を提供します。追加の層により、

RF、デジタル、電源セクションを完全に分離し、優れたシールドのために複数のグランドプレーンを提供します。

mmWave向けに最適化された12層構成:

∙ レイヤー 1: RF 信号レイヤー A (mmWave アンテナ給電、マイクロストリップ 50Ω) ∙ レイヤー 2: グランドプレーン A (プライマリ RF リターン、1 オンス Cu)

∙ レイヤー3: RF信号レイヤーB(セカンダリRFパス、ストリップライン50Ω)

∙ レイヤー4: グランドプレーンB(RF絶縁およびリターン、1オンスCu)

∙ レイヤー5: 電源プレーンA (RF電源: +5V PA電源、2オンスCu)

∙ レイヤー6: 高速デジタル (SerDes、DDR、PCIe ストリップライン)

∙ レイヤー7: 高速デジタル(レイヤー6への直交ルーティング)

∙ レイヤー 8: 電源プレーン B (デジタル電源: +3.3V、+1.8V、+1.2V 分割、2 オンス Cu) ∙ レイヤー 9: グランドプレーン C (デジタルリターンとシールド、1 オンス Cu)

∙ レイヤー 10: 低速信号とルーティング (制御、I2C、SPI)

∙ レイヤー11: グランドプレーンD(最終シールド層、1オンスCu)

∙ 第12層:RF信号層C(二次RF、部品配置、マイクロストリップ50Ω) このSGSGPSSPGSGS構成は卓越した性能を提供します。4つの独立したグランドプレーンが多重シールドバリアを形成し、RF層はデジタルスイッチングノイズから完全に分離され、L3のストリップラインRF配線は敏感なパスに対して優れたシールドを提供します。スタックアップはL6-L7中心プレーンを中心として対称性を維持します。

図5 – 12層5G PCBスタックアップの詳細な断面図。層の厚さ、銅の重量、信号/プレーンを示しています。

5. 5G PCBの接地技術

5.1 高周波設計における接地の基礎

高周波において、グラウンドは単なるゼロ電圧基準点ではなく、複雑な電磁気構造であり、その挙動は信号整合性性能を左右します。基本原理:高周波のリターン電流は、関連する信号トレースの真下を、最小インピーダンスの経路に沿って流れます。この経路は直流抵抗ではなくインダクタンスに依存し、リターン電流は信号導体との磁界結合が最大となる領域に自然に集中します。

ミリ波周波数における表皮効果により、リターン電流はグランドプレーン表面から数百ナノメートルの層にのみ流れます。そのため、表面仕上げと酸化電位は驚くほど重要になります。変色した銅は、光沢のある銅よりも高いRF耐性を示します。そのため、多くの設計者は、ニッケル層によってわずかにインダクタンスが増加するにもかかわらず、重要なRF領域のグランドプレーンにENIG(無電解ニッケル浸漬金)表面仕上げを指定します。

5.2 ソリッドグランドプレーンの実装

途切れることのない連続したグランドプレーンは、高周波PCBスタックアップにおいて最も重要な要素です。グランドプレーンは、リターン電流が流れるための完全に滑らかな湖面を提供すると考えてください。障害物(ボイド、スロット、切り欠きなど)は乱流を引き起こし、エネルギーを放射したり信号を反射したりします。5Gアプリケーションでは、グランドプレーンの完全性は不可欠です。すべてのグランドプレーンは、基板の端から端まで、最小限の途切れで広がる必要があります。

アナログ部とデジタル部を分離するため、あるいは取り付け穴周辺の放熱のためにグランドプレーンの分割が避けられない場合は、スティッチングコンデンサを使用してギャップを埋めます。分割部に沿って0.1μF以下のコンデンサを1~2インチ間隔で配置することで、DC絶縁を維持しながらRF周波数でのAC短絡を確保します。高速信号やRF信号はグランドプレーンの分割部をまたいで配線しないでください。配線が分割部を横切る必要がある場合は、ループ面積を最小限に抑えるために垂直に配線し、交差点のすぐ隣にグランドビアを追加してください。

5.3 ビアステッチングとグラウンドフェンシング技術

ビアステッチング、すなわち層間のグランドプレーンを接続するためのグランドビアの戦略的な配置は、5G PCB設計において最も重要でありながら、しばしば見落とされがちな側面の一つです。ミリ波周波数では、短いグランド接続であってもインダクタンスが顕著になります。厚さ62ミルの基板に直径10ミルのビア1つが通るだけで、約0.7nHのインダクタンスは一見無視できる程度ですが、28GHzでは約123オームのインピーダンスとなり、高周波グランド接続を著しく劣化させるのに十分な値となります。

解決策は並列ビアアレイです。4つのビアを並列に使用すると、実効インダクタンスが約4分の1に減少し(相互インダクタンスの影響を考慮)、接続インピーダンスがより許容できるレベルになります。重要なRFコンポーネントの場合は、各グランドピンのすぐ隣に3~4個のグランドビアを配置し、最も近いグランドピンに接続します。

ソリッドグラウンドプレーン。これらのビアはコンポーネントにできるだけ近づけて配置してください。ビアの長さに応じてインダクタンスが増加するため、短い経路が不可欠です。

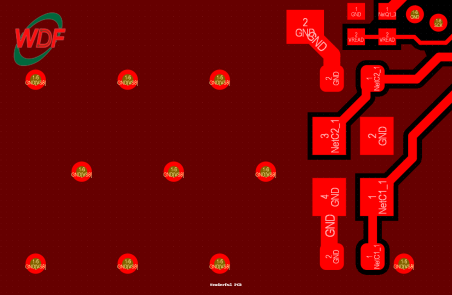

図6 – PCBレイアウトの上面図。ビアステッチングパターンが周囲に表示されている。

6. 5Gスタックアップにおけるインピーダンス制御

6.1 制御インピーダンスの基礎

インピーダンス制御は、高速およびRF信号の完全性(インテグリティ)の基盤となります。信号源、伝送経路、終端のすべてが同じ特性インピーダンスを示す場合、エネルギーは反射なく信号源から負荷へ完全に伝達されます。インピーダンスの不整合があると、信号の一部が信号源に向かって反射し、定在波、リンギング、符号間干渉(ISI)が生じ、デジタル信号が劣化し、RFシステムの性能が低下します。

5Gアプリケーションでは、50ΩのシングルエンドインピーダンスがRFおよびマイクロ波回路の標準となっています。この値は、同軸ケーブルの電力処理能力と損失の最適化から生まれたものであり、RFエコシステム全体、コネクタ、試験装置、コンポーネントは50Ωシステムを前提としています。

高速デジタルインターフェースでは、通常、50 オームシングルエンド(クロックなどのシングルエンド信号の場合)または 100 オーム差動インピーダンス(MIPI、PCIe、USB などの差動ペアの場合)が使用されます。

6.2 RF信号用マイクロストリップ構成

基板の外層にある信号トレースと、隣接する内層にあるグランドプレーンを繋ぐマイクロストリップは、RF 回路で最も一般的な伝送線路構成です。

マイクロストリップの特性インピーダンスは、トレース幅(W)、グランドプレーンからの高さ(H)、銅の厚さ(T)、および基板材料の誘電率(εr)に依存します。一次近似では、トレース幅が広く誘電体が厚いほどインピーダンスは増加し、誘電率が高いほどインピーダンスは減少します。

マイクロストリップの計算例:厚さ5ミルのRogers RO4350B(εr = 3.48)で1オンスの銅箔を使用して50Ωを実現するには、約11ミルのトレース幅が必要です。4ミルの誘電体で同じインピーダンスを実現するには、8.5ミルの幅が必要です。これは、誘電体の厚さに対する感度を示しています。

図7 – マイクロストリップ伝送線路の断面図

6.4 高速インターフェースの差動ペアインピーダンス

2つの相補信号間の電圧差としてデータを伝送する差動信号方式は、優れたノイズ耐性とEMIの低減により、現代の高速デジタルインターフェースで主流となっています。差動インピーダンス(Zdiff)は、各トレースのシングルエンドインピーダンス(Z0)とトレース間の結合度の両方に依存します。疎結合のトレースの場合、Zdiff ≈ 2 × Z0となります。トレースが近づくにつれて結合度が増加し、差動インピーダンスはこの2:1の比率を下回ります。

100Ωの差動インピーダンス(ほとんどの高速デジタルインターフェースの標準)を実現するには、一般的な設計では50Ωのシングルエンド配線を使用し、カップリングによって差動インピーダンスを100Ωに低減します。エッジカップリング配線のマイクロストリップ線路では、100Ωの差動インピーダンスを実現するには、通常、配線幅の1.5~2倍の配線間隔が必要です。間隔が狭くなるとカップリングが増加し、差動インピーダンスがさらに低下します。一方、間隔が広くなるとカップリングが減少し、差動インピーダンスが上昇します。

| 層 | 演算 | タイプ | 銅重量 | 厚さ | 材料 |

| L1 | RF信号 | マイクロストリップ 50Ω | 0.5オンス | – | RO4350B |

| L2 | 陸上 | 飛行機 | 1オンス | 5千 | ペース: |

| L3 | RF信号 | ストリップライン 50Ω | 0.5オンス | 6千 | プリプレグ |

| L4 | 陸上 | 飛行機 | 1オンス | 8千 | ペース: |

| ... | 対称 | 鏡 | ... | ... | ... |

表2: 最上層を示す12層5Gスタックアップ構成の例(一部)

7. シグナルインテグリティに関する考慮事項

5G PCBにおけるシグナルインテグリティは、適切に管理されなければシステム性能を低下させる可能性のある、相互に関連する複数の現象を包含しています。信号劣化のメカニズムとそれを軽減するスタックアップ設計手法を理解することで、機能的な設計と最適な設計を区別することができます。

7.1 高周波損失のメカニズム

信号損失は、複数の物理的影響により、周波数の上昇とともに劇的に増加します。誘電損失は、基板材料の分子分極によって発生します。これは、電界がRF周波数で振動し、材料内の双極子が電界に沿おうとすることでエネルギーを熱として消散させるためです。この損失は誘電正接と直接相関しており、誘電正接(Df)が2倍になると損失も約2倍になります。28GHzでは、標準FR-4(Df ≈ 0.020)では誘電損失が1インチあたり1.5dBを超える可能性があります。一方、Rogers RO3003(Df ≈ 0.001)では、同一条件下で0.3dB/インチ未満の損失を実現しています。導体損失は、表皮効果により周波数の平方根に比例して増加します。表皮効果とは、高周波電流が導体表面付近に集中し、実効抵抗が増加する現象です。

7.2 mmWaveアプリケーション向けビア設計

ビアスタブは、スルーホールビアの未使用部分が信号出口層を超えて伸び、特定の周波数で信号を反射する共振構造を形成します。スタブは短絡伝送線路として機能し、1/4波長共振によって反射が最大になります。28GHz、基板厚50ミルの場合、15ミルのスタブでさえ問題となる共振を引き起こす可能性があります。解決策としては、バックドリル加工でスタブを除去するか、信号層で終端するブラインドビア/ベリードビアを使用することが挙げられます。

図9 – バックドリルPCBビア

結論

5G PCBスタックアップ設計を成功させるには、材料科学、電磁気学、製造プロセス、熱管理など、複数の分野の専門知識が必要です。この記事で紹介するガイドラインは、材料選定から接地戦略、インピーダンス制御に至るまで、高品質な5G PCBスタックアップ設計を実現するための包括的な枠組みを提供します。

パフォーマンス 5G 設計。

主な成果は次のとおりです:

1. 材料の選択によってパフォーマンスとコストが決まります。必要な場合には高周波ラミネートを使用し、その他の場合には FR-4 を使用します。

2. 適切なリファレンスプレーンを備えた対称的なスタックアップは必須です。3. グランドプレーンの整合性とビアスティッチングによって、mmWave における信号の整合性が決まります。

4. インピーダンス制御には、誘電体の厚さの正確な制御とフィールド ソルバーの検証が必要です。

5. PCB メーカーとの早期の連携により、コストのかかる再スピンを回避できます。

5Gテクノロジーは高周波数化と複雑化へと進化を続けますが、ここで概説した手順と手法は今後も基本的なものとして残ります。初めての5G製品を設計する場合でも、既存のプラットフォームを最適化する場合でも、スタックアップの最適化に時間を投資することで、システム性能、製造歩留まり、そして市場投入までの期間短縮に大きなメリットがもたらされます。