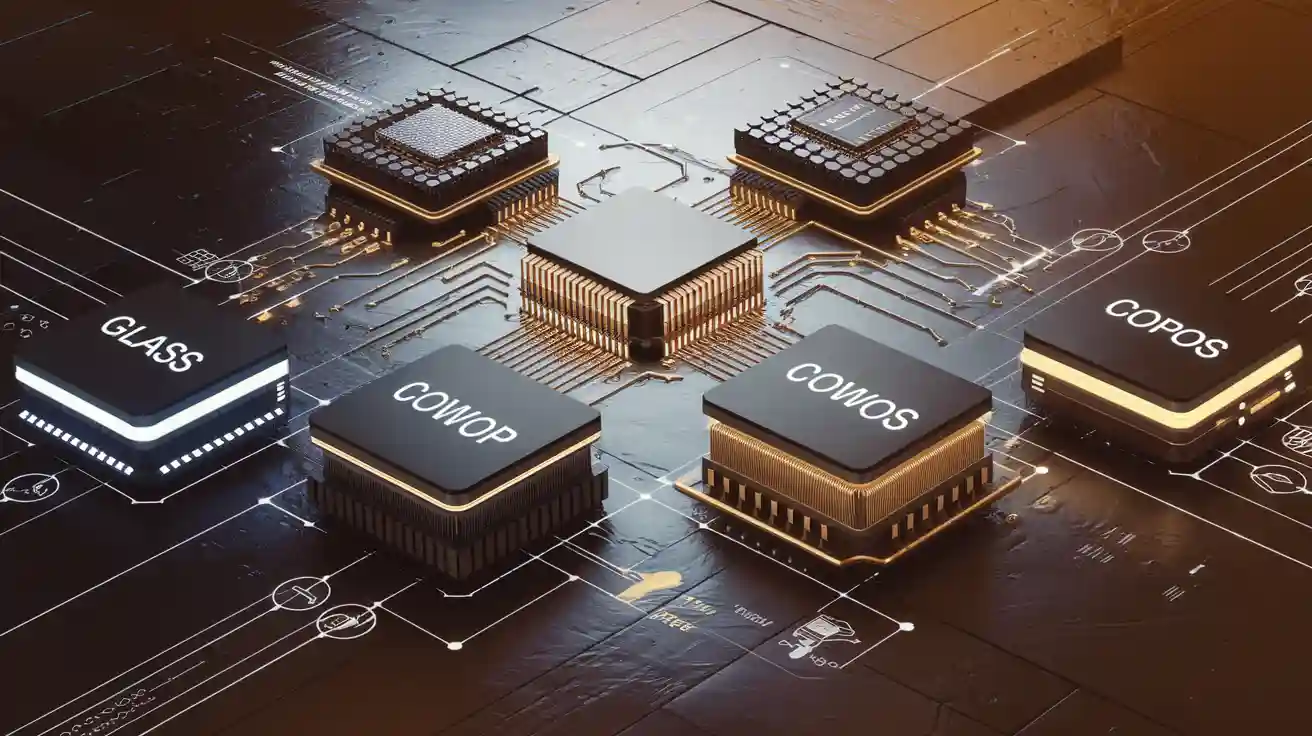

チップに最適なパッケージング技術を選択する必要があります。半導体業界では現在、ガラス、CoWoP、CoWoS、CoPoSといった新しいソリューションが生まれています。それぞれが独自の部品接続方法を持ち、特別な性能上の利点をもたらします。ガラス基板は高度なパッケージングを可能にし、信号の伝送速度を向上させます。半導体業界は、世界のニーズに応えるため、部品をより効率的に組み立てる方法の開発に取り組んでいます。技術は変化し続け、より多くのチップを使用し、コストを削減しています。お客様の選択によって、半導体業界におけるチップとPCBの接続方法が変わります。

テクノロジーの基礎

ガラス基板

ガラスはチップの製造方法を変えています。 ガラスコア基板 ガラスは信号の伝送速度を速め、消費電力も削減します。ガラスはチップに平坦で強固な基盤を提供します。ガラスを使用することで、狭い面積に多くの接続部を収容できます。高性能チップにはガラスコア基板が使用されています。ガラスは技術の高速化と冷却に貢献します。ガラス基板は、ファンアウト型ウェーハレベルパッケージング(WLP)やFOLP(フォップラーパッケージ)に使用されています。ガラスは、高度なチップパッケージングにおける課題の解決に役立ちます。

ヒント: ガラス コア基板を使用すると、より多くの部品を収容でき、高度なパッケージングでより優れたパフォーマンスを実現できます。

CoWoSの概要

CoWoSは、先端パッケージングにおける大型チップに使用されます。チップをウェハ上に積層し、基板上に配置します。CoWoSはメモリチップとロジックチップを接続します。サーバーやAIチップにCoWoSが採用されています。CoWoSは高速化と低消費電力化を実現します。先端パッケージングにおける広帯域化に使用されます。CoWoSはガラス基板やフォップラップ(foplp)で動作します。CoWoSは新しいチップパッケージングにおいて重要な役割を果たします。

CoPoSとCoWoP

CoPoSは、 高度なチップパッケージングチップを大型パネルに実装し、基板に接続します。CoPoSはコスト削減とスケーリングの容易化に役立ちます。ガラスコア基板とfoplpで動作します。CoWoPはファンアウト型ウェハレベルパッケージングとfowlpに使用されます。CoWoPは新しい技術でチップをPCBに接続します。業界では、柔軟で拡張性の高いパッケージングにCoWoPが使用されています。CoPoSとCoWoPは、チップに最適な技術の選択に役立ちます。

構造の比較

基板材料

それぞれの技術の特徴を理解することが重要です。基板はチップの基盤となるものです。パネルレベルのパッケージングには、多くの選択肢があります。 ガラスコア基板 ガラスは平らで丈夫なため人気があります。ガラスは回路を滑らかに配置できるため、狭いスペースに多くの回路を収めることができます。これにより、チップの動作速度が向上します。また、ガラスは熱や電力消費を抑える効果もあります。

CoWoSはシリコンまたは有機基板を使用します。CoWoSは多くのチップ設計に利用されており、チップ・オン・ウェーハ・オン・サブストレート方式をサポートしています。CoPoSとCoWoPはパネルレベルのパッケージングを採用することでコストを削減し、パネルの大型化にも貢献します。CoPoSではガラスコア基板が使用されることが多く、CoWoPではガラスまたは有機材料を使用できます。

注: ガラス コア基板により、高度なパッケージングにおいて信号の移動が高速化し、消費電力が削減されます。

インターポーザーとパネルの違い

それぞれの技術がどのようにチップを接続するかを見てみましょう。CoWoSはインターポーザーを使用します。インターポーザーはチップと基板の間に配置され、メモリチップとロジックチップの接続に役立ちます。CoWoSは高速接続のためにシリコンインターポーザーを使用します。

パネルレベルのパッケージングは異なります。CoPoSとCoWoPは、ウェハではなく大型パネルを使用します。これにより、パネルにより多くのチップを配置できます。これによりコストが削減され、より多くのチップを製造できます。CoPoS(チップ・オン・パネル・オン・サブストレート)は、ガラスコア基板を使用することで優れた性能を発揮します。CoWoPは、パネルレベルのパッケージングを使用してチップを基板に直接接続します。

CoWoS: シリコン インターポーザーを使用し、高速チップに適しています。

CoPoS: ガラスコア基板と大型パネルを使用し、パネルレベルのパッケージングに最適です。

CoWoP: パネルレベルのパッケージングを使用し、シリコンインターポーザーなしでチップを接続します。

パネルレベルのパッケージングにより、一度に多くのチップを製造できます。これにより、より良い結果とより低いコストが実現します。ガラス、CoWoS、CoPoS、CoWoPはすべて、新しいチップ設計に役立ちます。

パフォーマンスとチップ

信号と電力

チップには、高速データ転送と省電力が求められます。適切なパッケージング技術は、これらの目標達成に役立ちます。ガラス基板は表面が平坦なので、 信号が伝わる 損失が少なく、チップの性能が向上します。CoWoSはシリコンインターポーザーを使用し、メモリとロジックチップ間の信号を強力に保ちます。これは、速度が1ビットたりとも重要でない高性能コンピューティングでよく見られます。

CoPoSとCoWoPはパネルレベルの統合を採用しています。2.5枚のパネルにより多くのチップを搭載できるため、システムレベルの統合性が向上します。この構成により、スペースの節約と電力効率の向上が期待できます。3D/XNUMXDスタッキング技術により、チップを近接して積み重ねることができます。これにより、信号経路が短縮され、消費電力が低減されます。半導体製品のパフォーマンスと効率が向上します。

注: 適切な統合とは、チップ間の通信速度が速くなり、消費電力が少なくなることを意味します。

熱と信頼性

熱はチップの動作速度を低下させたり、損傷させたりする可能性があります。そのため、熱を素早く放出するパッケージが必要です。ガラス基板は熱を効果的に拡散するため、チップの温度を低く保ちます。これにより、半導体デバイスの寿命が長くなります。CoWoSも、シリコンインターポーザーがチップから熱を逃がすため、熱対策に役立ちます。

CoPoSとCoWoPは大型パネルを採用し、チップを広範囲に配置できます。これにより、熱管理が容易になります。チップが過熱しないため、信頼性が向上します。また、優れた統合性により、脆弱な箇所も少なくなり、半導体製品の寿命が長くなります。チップは長年良好な状態で動作することが求められますが、適切なパッケージングはその目標達成に役立ちます。

ガラス: 熱を拡散し、チップを安定させます。

CoWoS: 主要チップから熱を逃がします。

CoPoS/CoWoP: パネルスペースを使用して熱を管理し、信頼性を高めます。

コストと製造

プロセスの複雑さ

それぞれがどれだけ複雑であるかを見る必要があります 包装プロセス 適切なものを選ぶ前に、まずは適切なものを選ぶことが重要です。ガラス基板は特殊な工具を必要とする新しい手法を採用しています。ガラスは割れる可能性があるため、慎重に取り扱う必要があります。そのため、パッケージング工程が難しくなり、場合によっては時間がかかることもあります。CoWoSはシリコンインターポーザーを使用するため、工程が増えます。チップを積み重ね、細い配線で接続する必要があります。そのため、パッケージング工程はより複雑になり、コストも高くなります。

CoPoSとCoWoPの使用 パネルレベルパッケージングより大きなパネルを扱えるため、一度に多くのチップを製造できます。これにより時間を節約できます。パネルレベルパッケージングのプロセスは、インターポーザーを用いた積層よりも複雑ではありません。必要な工程数も少なくて済みます。ガラスパネルや有機パネルを使用できるため、プロセスに柔軟性が生まれます。

ヒント: プロセスをシンプルにしたい場合は、CoPoS や CoWoP などのパネル レベルのパッケージングを使用すると、より早く完了できます。

拡張性

パッケージはニーズに合わせて拡張する必要があります。ガラス基板は、小さなスペースに多くの接続部を収容できるため、高性能チップの製造に役立ちます。チップのニーズの拡大に合わせて設計をスケールアップできます。CoWoSは大型で高性能なチップに適していますが、プロセススケールは容易ではありません。ウェハとインターポーザーを使用する必要があるため、一度に製造できるチップの数が制限されます。

CoPoSとCoWoPは、多数のチップを製造する必要がある場合に最適です。パネルレベルのパッケージングにより、大型パネルを使用できます。これにより、バッチごとにより多くのチップを製造できます。これによりコストが削減され、大量注文にも対応しやすくなります。パネルレベルのパッケージングにより、柔軟性が向上します。プロジェクトに合わせてパネルのサイズや材料を変更できます。

ガラス: 高密度、高性能のパッケージングに適しています。

CoWoS: トップエンドのチップに最適ですが、スケーラビリティは低くなります。

CoPoS/CoWoP: 大量生産や柔軟なパッケージングのニーズに最適です。

注: チップ事業の拡大を計画している場合、パネル レベルのパッケージングがスケールアップに最適な方法となります。

PCBの影響

設計の柔軟性

テクノロジーの進化に合わせてPCB設計も変化させたいものです。パネルレベルのパッケージングは、従来の方法よりも多くの選択肢を提供します。大きなパネルを使用すれば、多数のチップをまとめて実装できます。これにより、PCBのサイズや形状を簡単に変更できます。ガラス基板を使用すれば、回路を小型化し、より多くのリンクを追加できます。foplpやfowlpを使用すれば、洗練されたレイアウトを実現できます。これらの方法により、基板により多くの機能を搭載できます。

パネルレベルパッケージングは、シンプルな設計から複雑な設計まで幅広く対応します。ジョブごとに異なるパネルサイズを選択できます。これにより、新しいチップに合わせて設計変更が容易になります。FOLPとガラス基板は、高密度回路の構築に役立ちます。これにより、速度が向上し、設計の選択肢が広がります。

ヒント: パネル レベルのパッケージングにより、新しいチップ スタイルや設計の変更に対応できるようになります。

組み立ての必要性

PCBにチップを配置する容易さについて考える必要があります。パネルレベルのパッケージングは、組み立てをより迅速かつ容易にします。1枚のパネルに多くのチップを配置できるため、時間の節約になります。また、組み立て時のミスも削減できます。 ガラス基板はパネルを平坦に保つのに役立ちます、より良いリンクを取得できます。

パネルレベルパッケージングは、foplpとfowlpの両方でうまく機能します。これらの方法を使用することで、構築をよりスムーズに行うことができます。このプロセスは、大量のボードを製造するのに適しています。速度が向上し、コストも削減されます。従来の方法ほど多くの手順を必要としません。これにより、 組立ライン作業 より良い。

パッケージングタイプ | 組み立て速度 | 設計の柔軟性 | 効率化 |

|---|---|---|---|

パネルレベルのパッケージング | ハイ | ハイ | ハイ |

伝統的な包装 | ロー | ロー | ロー |

注: パネル レベルのパッケージングにより、今日の PCB に最適な速度、柔軟性、効率の組み合わせが実現します。

Glass vs CoWoP vs CoWoS vs CoPoS

主な違い

それぞれのテクノロジーが特別なものである理由を理解することが重要です。 CoWoS はシリコンインターポーザーを使用します 高度なチップを接続するために、CoPoSはパネルレベルのパッケージングで大型パネルを使用します。これにより、一度に多くのチップを製造でき、コストを削減できます。CoWoPもパネルレベルのパッケージングを使用しますが、シリコンインターポーザーは使用しません。これにより、プロセスがより簡単かつ迅速になります。ガラス基板は、高度なパッケージングのための平坦で強固な基盤を提供します。これにより、より優れた信号とより多くのリンクを、狭いスペースで実現できます。

主な機能を比較するのに役立つ表を以下に示します。

テクノロジー | Structure | パフォーマンス | 費用 | PCBの影響 |

|---|---|---|---|---|

コワス | シリコンインターポーザー、ウェーハベース | 高度なチップでは高い | ハイ | ハイエンドボードに最適 |

コポス | パネルレベルのガラス基板 | 高い拡張性 | 低くなる | 柔軟性が高く、多くのチップをサポート |

コワップ | パネルレベル、インターポーザーなし | 良い、シンプル | 低くなる | 簡単な組み立て、柔軟な設計 |

Glass | 平らで丈夫な基板 | 高度なパッケージングに最適 | 技法 | タイトなレイアウトをサポート |

ヒント: CoWoS は高度なチップに最高速度をもたらしますが、CoPoS と CoWoP はより多くのチップを製造し、コストを節約するのに役立ちます。

アプリケーションの適合性

作業内容に合わせて適切なパッケージを選ぶ必要があります。ハイエンドチップを使用する場合は、CoWoSが最高の速度とチップリンクを提供します。CoPoSは、多くのチップを低コストで製造したい場合に適しています。CoWoPは、シンプルな設計と迅速な構築に適しています。 ガラス基板は高性能を実現します 多数のチップを接続します。

業界では当初、強力なチップ接続のためにCoWoSが採用されていました。現在では、より大規模なバッチ処理と低コスト化のために、CoPoSやCoWoPを使用する企業が増えています。この変化において、ガラス基板は重要な役割を果たしています。技術の進歩に伴い、チップの接続方法やパッケージング方法も増えています。

注: チップのニーズ、予算、チップをどの程度接続したいかを考慮して、最適なテクノロジを選択してください。

課題と機会

技術的な障壁

チップの高度なパッケージングには多くの問題があります。ガラス基板は製造工程で破損する可能性があり、ガラスを扱うには特殊な工具が必要です。CoWoSではシリコンインターポーザーを使用するため、工程が増え、チップの組み立てが難しくなります。CoPoSとCoWoPでは大型パネルを使用しますが、パネルを平坦かつ清潔に保つ必要があります。そうしないと、チップが正常に動作しない可能性があります。

半導体業界は歩留まりにも問題を抱えています。パネル上の多くのチップがテストに合格しないこともあります。これは良品チップの減少とコスト上昇を意味します。製造中は埃や熱を遮断しなければなりません。世界はより多くのチップを求めていますが、これらの問題が製造を遅らせています。高度なパッケージングを行うには、新しい機械を使いこなすための訓練が必要です。ガラスなどの新しい材料の使用は、さらに多くの問題をもたらします。

注: 半導体業界は、世界のチップ需要に応えるためにこれらの問題を解決する必要があります。

今後の動向

半導体業界にはまもなく大きな変化が訪れます。世界はより高速でより小型のチップを求めています。高度なパッケージングは、これらの目標達成に貢献します。より良い結果を得るために、より多くのガラス基板を使用することになります。新しいツールによって、チップの組み立てはより容易になります。半導体業界では、作業をスピードアップするために、より多くの機械が導入されるでしょう。

AIや高性能チップには高度なパッケージングが必要です。データセンターやスマートデバイスでは、CoWoSやCoPoSがますます多く見られるようになるでしょう。市場の成長に伴い、これらの技術は世界中でさらに活用されるでしょう。チップの接続方法や熱制御の新たな方法が見つかるでしょう。半導体業界は、チップの製造と接続のより優れた方法を常に模索し続けるでしょう。

高度なパッケージングは、より優れた AI チップの製造に役立ちます。

世界はもっと必要とするだろう 熟練労働者 チップ用。

半導体業界は、より優れたチップ製造のために新しい材料を使用します。

ヒント: 世界のチップ市場で先頭に立つには、半導体業界の新しいトレンドに注目してください。

適切なテクノロジーの選択

高性能チップ

チップは高速で、大きな処理能力を持つことが求められます。半導体業界は毎年新しいソリューションを生み出しています。ハイエンドチップを使用する場合は、高度なパッケージングが必要です。CoWoSはまさにこれに最適です。メモリチップとロジックチップをしっかりと接続します。CoWoSはシリコンインターポーザーを使用しており、これによりチップ間のデータ共有が高速化されます。半導体業界では、AI、サーバー、データセンターなどでCoWoSが使用されています。

ガラス基板は、困難な目標の達成にも役立ちます。小さなスペースに多くのリンクを収めることができるため、チップはより高速にデータを転送できます。ガラスパッケージは熱制御に優れており、チップは低温に保たれ、良好な動作を実現します。半導体業界では、これらの方法を用いてチップの最高速度を実現しています。

ヒント: 最も速いチップを選ぶには 高度な包装 CoWoSやガラス基板など。これらの選択肢により、速度と強力なチップ接続が実現します。

コスト重視の用途

時々あなたはする必要があります お金を節約する チップ製造において、半導体業界はより安価なチップ製造方法を模索しています。CoPoSとパネルレベルパッケージングはコスト削減に貢献します。一度に多数のチップを製造できるため、大型パネルやガラス基板を使用する場合もあります。多額の費用をかけずに、良好なチップ接続を実現できます。

CoWoPはコスト削減にも役立ちます。シリコンインターポーザーは不要で、プロセスは簡単かつ迅速です。半導体業界では、電子機器やその他の安価な製品にこの手法が採用されています。優れた機能を実現しながらコストを抑えることができます。

テクノロジー | 以下のためにベスト | コストレベル | 統合レベル |

|---|---|---|---|

コワス | 高性能チップ | ハイ | 高機能 |

コポス | 大量生産 | ロー | 高機能 |

コワップ | シンプルで高速なビルド | ロー | グッド |

ガラス基板 | 高度な統合 | 技法 | 高機能 |

注:コストを抑えつつ優れた機能を実現したい場合は、CoPoS、CoWoP、またはガラス基板をお試しください。半導体業界では、多くの種類のチップにこれらが使用されています。

高度なパッケージングが将来のチップをどう変えるのか、お分かりいただけると思います。CoWoSは、超高速チップが必要な場合に最適です。CoPoとCoWoPは、より少ないコストでより多くのチップを製造できます。半導体業界は、人々のニーズを満たすためにこれらの新しい方法を活用しています。パッケージングを選ぶ際には、チップの機能、コスト、そして将来的に必要になる可能性のあるものについて考えてみてください。半導体業界は、今後も常に新しく、より良いアイデアを生み出し続けるでしょう。

FAQ

ガラス基板を使用する主な利点は何ですか?

ガラス基板 平らで強固なベースを提供します。小さなスペースで、より高速な信号速度とより多くの接続を実現します。これにより、チップの動作が高速化し、冷却効果も高まります。

CoWoS と CoPoS の違いは何ですか?

CoWoSはシリコンインターポーザーを使用してチップを接続します。これにより、高速かつ強力な接続が可能になります。CoPoSは大型パネルとガラス基板を使用します。これにより、一度に多くのチップを製造でき、コストを削減できます。

高性能チップにパネルレベルパッケージングを使用できますか?

はい、高性能チップにはパネルレベルパッケージングを使用できます。優れた速度が得られ、一度に多数のチップを製造できます。この方法はコスト削減にも役立ちます。

企業が一部の製品に CoWoP を選択するのはなぜでしょうか?

企業は、シンプルかつ迅速な構築を求める際にCoWoPを選択します。シリコンインターポーザーは不要です。これにより、プロセスが簡素化され、コストも削減されます。

パッケージング技術を選択する際に考慮すべきことは何ですか?

チップのニーズ、予算、そして製造したいチップの数を検討する必要があります。速度、コスト、そしてチップの接続方法についても検討しましょう。