DIPの概要

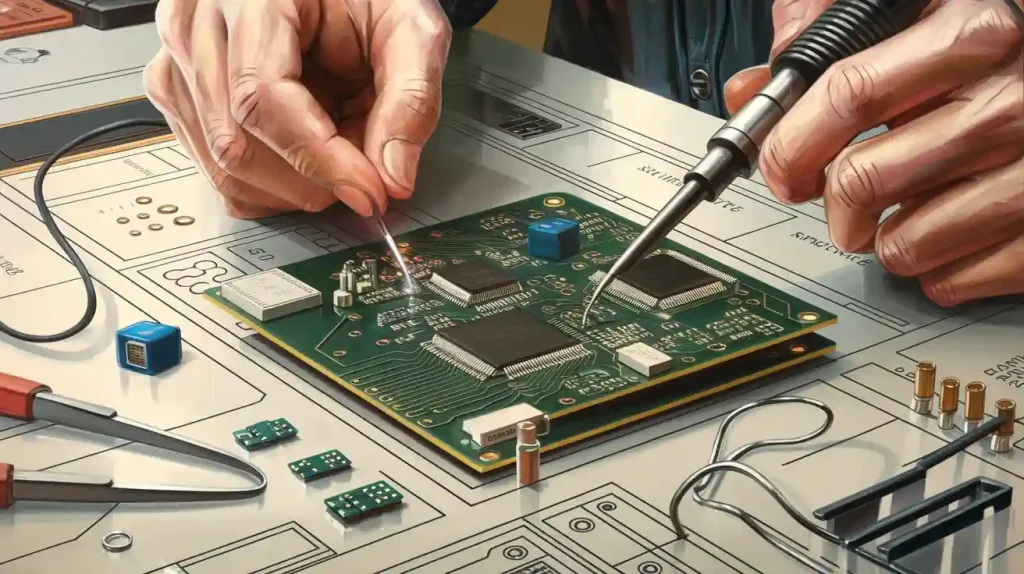

DIPはプラグイン方式です。このパッケージング方法を採用したチップは2列のピンを備えており、DIP構造のチップソケットに直接はんだ付けするか、同じ数のはんだ穴を持つはんだ付け位置にはんだ付けすることができます。PCB基板の穴あきはんだ付けを容易に実現でき、マザーボードとの互換性も良好であるという特徴があります。しかし、パッケージ面積が大きく厚みがあるため、挿抜時にピンが損傷しやすく、信頼性が低いという欠点があります。

DIPは最も一般的なプラグインパッケージであり、その応用範囲は標準ロジックIC、メモリLSI、マイコン回路などを含みます。スモールアウトラインパッケージ(SOP)。派生パッケージにはSOJ(Jピンスモールアウトラインパッケージ)、TSOP(薄型スモールアウトラインパッケージ)、VSOP(超小型アウトラインパッケージ)、SSOP(シュリンクSOP)、TSSOP(薄型シュリンクSOP)、SOT(スモールアウトライントランジスタ)、SOIC(スモールアウトライン集積回路)などがあります。

DIPデバイスアセンブリの設計上の欠陥

1. 大きなPCBパッケージ穴

PCBのプラグイン穴とパッケージピン穴は仕様書に基づいて設計されます。製版工程では、穴に銅メッキを施す必要があり、一般的な公差は±0.075mmです。PCBのパッケージ穴が実機のピンよりも大きい場合、デバイスの緩み、錫メッキ不足、空はんだなどの品質問題が発生する可能性があります。

下図をご覧ください:WJ124-3.81-4P_WJ124-3.81-4P(KANGNEX)のデバイスピンは1.3mm、PCBパッケージの穴は1.6mmです。穴径が大きいため、ウェーブソルダリング時に空はんだが発生します。

上図に引き続き、設計要件に従ってWJ124-3.81-4P_WJ124-3.81-4P(KANGNEX)コンポーネントを購入し、ピン1.3mmが正しいです。

2. 小さなPCBパッケージ穴

- PCB基板のプラグイン部品のはんだ付けパッドの穴が小さく、部品を挿入できません。この問題を解決するには、穴の直径を拡大してからプラグを挿入するしかありませんが、穴の中に銅はありません。この方法は、片面または両面基板の場合に使用できます。片面または両面基板の外層は導電性があり、はんだ付け後に導通することができます。多層基板のプラグイン穴が小さく、内層が導電性の場合、穴を拡大しても内層の導通を改善できないため、PCB基板をやり直すしかありません。

下図をご覧ください:設計要件に基づき、A2541Hwv-3P_A2541HWV-3P(CJT)の部品を購入しました。ピンは1.0mmですが、PCBパッケージのパッド穴は0.7mmのため、挿入できません。

上図に続き、設計要件に基づき、A2541Hwv-3P_A2541HWV-3P(CJT)の部品を購入しました。ピン径は1.0mmが正解です。

3. PCBパッケージのピン間の距離が部品と一致していない

DIP デバイスの PCB パッケージ パッドは、ピンと同じ穴径を持つだけでなく、ピン間の間隔も同じ距離である必要があります。

ピン穴間隔とデバイス間の不一致により、ピン間隔を調整できるコンポーネントを除き、デバイスを挿入できなくなります。

下図をご覧ください:PCBパッケージのピンホール間隔は7.6mmですが、購入した部品のピンホール間隔は5.0mmです。この2.6mmの差により、デバイスは使用できなくなります。

4. PCBパッケージの穴間隔が狭すぎるため、錫の短絡が発生する

パッケージの設計・製図においては、ピンホール間の距離に注意する必要があります。たとえピンホール間隔が狭いベアボードを製造できたとしても、組み立て工程におけるウェーブソルダリング時に錫のショートが発生しやすくなります。

下図をご覧ください。ピン間隔が狭いと、錫ショートが発生する可能性があります。ウェーブはんだ付け時の錫ショートの原因は様々ですが、設計側で事前に実装性を防止できれば、問題の発生率を低減できます。

DIPデバイスのピンの錫が不足している実際のケース

材料のキーサイズとPCBパッド穴のサイズの不一致の問題

問題の説明: 製品 DIP をウェーブはんだ付けした後、ネットワーク ソケットの固定フット パッドの錫が著しく不足しており、空はんだになっていることが判明しました。

問題の影響:ネットワークソケットとPCBボードの安定性が低下し、製品の使用中に信号ピンにストレスがかかり、最終的には信号ピンの接続が切断され、製品の性能に影響を与える可能性があります。ユーザーの使用中に故障するリスクがあります。

問題の拡張ネットワークソケットの安定性が低く、信号ピンの接続性能が悪く、品質にも問題があるため、ユーザーに安全上の危険をもたらす可能性があり、最終的な損失は想像を絶するものです。

素晴らしいPCB DFMサービス アセンブリ解析はデバイスのピンをチェックします

wonderpcb DFMサービスのアセンブリ解析機能には、DIPデバイスのピンに対する特別な検査機能があります。検査項目には、スルーホールのピン数、THTピン数制限、THTピン数制限、THTピン特性などが含まれます。これらのピン検査項目は、基本的にDIPデバイスのピン設計における潜在的な問題を網羅しています。

設計が完了したら、wonderfulpcb DFM Servicesのアセンブリ解析を利用して、設計上の欠陥を事前に発見し、製品生産前に設計上の異常を解決します。これにより、アセンブリ工程中の設計上の問題、生産時間の遅延、研究開発コストの無駄を回避できます。