PCBエンジニアが製品のレイアウトを行う際には、部品の配置と配線だけにとどまりません。内層の電源プレーンとグランドプレーンの設計も同様に重要です。内層の管理には、パワーインテグリティ(PIM)、シグナルインテグリティ(SI)、電磁両立性(EMC)、そして製造性を考慮した設計(DFM)を考慮する必要があります。

内層と外層の違い

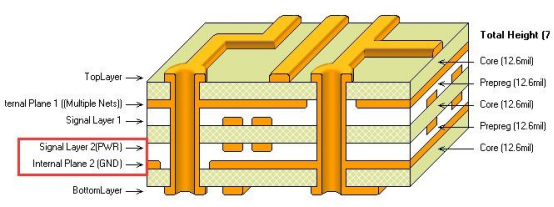

外層は配線や部品のはんだ付けに使用され、内層は電源プレーンとグランドプレーン専用です。これらの層は多層基板にのみ存在し、電源とグランドの経路を提供します。2層、4層、6層基板などの一般的な設計は、信号層と内部電源/グランド層の数によって決まります。

内層設計

1. 重要な信号の下のグランド層

高速信号、クロック信号、高周波信号の場合、これらの信号の真下にグランド層を配置すると、ループパスの長さが最小限に抑えられ、放射が低減されます。

2. 電源プレーンとグランドプレーン領域

高速回路設計では、電源プレーンからの放射とシステム干渉を最小限に抑える必要があります。通常、グランドプレーンが電源プレーンをシールドできるように、電源プレーンの面積はグランドプレーンよりも小さくする必要があります。一般的なルールとして、電源プレーンを内側に縮小することが挙げられます。 誘電体の厚さの2倍 地上面と比較して。

3. レイヤースタッキングプラン

電源プレーンは、対応するグランドプレーンに隣接して配置することでカップリング容量を形成します。デカップリングコンデンサと組み合わせることで、電源プレーンのインピーダンスを低減し、効果的なフィルタリングを実現します。

4. 参照面の選択

基準プレーンの選択は非常に重要です。電源プレーンとグランドプレーンはどちらも基準プレーンとして機能しますが、グランドプレーンは一般的に接地されているため、優れたシールド効果を発揮します。基準プレーンとしてはグランドプレーンが推奨されます。

5. エリア間ルーティングを避ける

隣接層における重要な信号は、セグメント化された領域をまたいではなりません。セグメント化をまたぐと大きな信号ループが発生し、大きな放射や結合が生じる可能性があります。

6. 電源とグランドの配線

グランドプレーンの整合性を維持してください。信号線をグランドプレーンに配線することは避けてください。信号密度が高い場合は、電源プレーンのエッジに沿って配線することを検討してください。

内層製造

内層の製造プロセスは、複雑なPCB製造ワークフローの一部に過ぎません。内層の製造では、積層や穴あけの許容誤差など、品質や歩留まりに影響を与える可能性のある他の工程も考慮する必要があります。特に多層PCBは、単層や二層基板に比べてより複雑なプロセスを必要とします。設計者は設計段階でこれらの複雑さを考慮する必要があります。

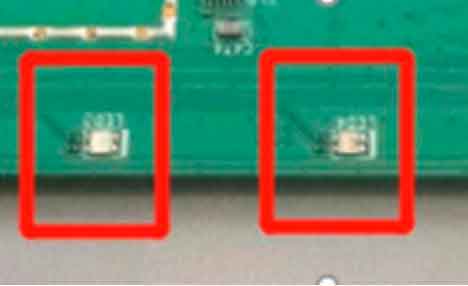

1. 非機能パッド(NFP)の取り外し

非機能パッド(NFP)とは、内層にある、どのネットワークにも接続されていないパッドのことです。PCB製造工程では、製品の機能には影響しませんが、品質と生産効率に影響を与える可能性があるため、NFPは除去されます。

(PIC-PCB内層-4)

2. BGAエリアの高密度ビアの取り扱い

BGAデバイスは、ピンが密集した小さなフットプリントを持つことが多く、ビアのファンアウトが密集しています。製造工程では、ラミネーションやドリル加工時の短絡を防ぐため、ビアはトレースや銅箔領域から安全な距離を保つ必要があります。ビア間の銅箔が保持されない場合、ネットワーク内で断線が発生する可能性があります。CAMエンジニアは、ビア間に銅箔ブリッジを追加することでこの問題に対処し、ネットワーク接続を確保する必要があります。

3. 内部層の設計異常に対処する

ネガフィルムを用いた内層設計において、全てのビアが銅箔から完全に分離されている場合、機能的な接続は実現されません。このような設計は内層を効果的に機能させません。メーカーは設計者に確認し、この設計が意図的なものなのか、それとも銅箔がネットワークに割り当てられていないのかを確認します。

4. ネガフィルムの内層におけるボトルネック

内層の電源プレーンとグランドプレーンの分割において、ビアの密集はネットワークの導電性にボトルネックを引き起こす可能性があります。電源ネットワークを接続する銅ブリッジが狭すぎると、十分な電流を流すことができず、基板の故障につながる可能性があります。深刻なケースでは、ボトルネックによって回路が断線し、設計上の欠陥につながる可能性があります。

これらの考慮事項に対処することで、PCB エンジニアは製造中の設計上の落とし穴を回避しながら、内部層の製造性と信頼性を高めることができます。