Du spørger måske, hvad VLSI-designcyklussen er. Denne proces hjælper dig med at lave en fungerende chip trin for trin. I meget storskala integration bruger man halvlederteknologi. Dette giver dig mulighed for at sætte millioner af transistorer på én chip. Hvert trin i cyklussen er vigtigt. Hvis du springer et trin over, kan du få fejl eller en chip, der ikke fungerer. VLSI-feltet er vokset meget hurtigt. Det globale marked var værd omkring 634.85 mia. USD i 2025Det kan nå op på 1,055.39 milliarder USD inden 2034. Man følger normalt disse hovedfaser i cyklussen:

Kravsamling

Design på systemniveau

RTL-design

Funktionel verifikation

Syntese

Sted og rute

Fysisk verifikation

Halvlederteknologi påvirker den elektronik, du bruger hver dag.

Specification

Specifikationsfasen er det første trin i VLSI-designcyklussen. Her bestemmer du, hvad chippen skal kunne. Du bestemmer også, hvor godt den skal fungere. Dette trin hjælper dig med at træffe gode valg senere. Hvis du udfører dette trin godt, vil din chip sandsynligvis fungere. Du kan også undgå store fejl og spare tid.

Krav

Du skal have klare krav før du starter VLSI-chipdesign. Disse krav fortæller, hvad chippen skal kunne. De fortæller også, hvor hurtig, hvor meget strøm og hvor stor chippen skal være. Du oplister alle de funktioner, chippen har brug for. At skrive disse detaljer hjælper alle med at kende målene. Det sikrer, at designet passer til det, folk ønsker.

Tip: Skriv kravene med enkle ord. Brug korte sætninger. Prøv at undgå svære ord.

Mange teams bruger forskellige måder at organisere deres krav på. Her er en tabel med nogle almindelige metoder:

Metode | Beskrivelse |

|---|---|

SystemVerilog | Har mange værktøjer til at kontrollere om chippen virker. Den bruger objektorienteret programmering og stikprøvekontrol. |

Universel verifikationsmetode (UVM) | Bruger SystemVerilog. Det hjælper teams med at bygge tests, der kan bruges igen. |

VHDL | Bruges meget til at skrive og kontrollere chipdesigns. Det hjælper med at modellere og teste hardware. |

e (Specman) | Har stærke værktøjer til at kontrollere chips. Den bruger stikprøvekontrol med regler. |

C/C++ og Python | Bruges til at fremstille testsystemer og testbænke. |

Systemmål

Du satte systemmål at hjælpe med at vejlede designet. Disse mål omfatter, hvor hurtig chippen skal være. De omfatter også, hvor meget den skal koste, og hvor meget strøm den kan bruge. Du bestemmer, hvordan chippen skal fungere sammen med andre enheder. Du planlægger også fremtidige ændringer. At sætte mål hjælper teamet med at holde sig på sporet.

Specifikationsfasen er meget vigtig i VLSI-chipdesign. Det lægger grundlaget for hele processen. En god specifikation sikrer, at chippen gør, hvad den skal. Dette er nøglen til, at projektet lykkes.

arkitektur

System Design

Du starter arkitekturfase ved at planlægge, hvordan din chip skal fungere. Du bestemmer, hvad hver del af chippen skal gøre. Du vælger også, hvordan disse dele skal kommunikere med hinanden. Dette trin hjælper dig med at opdele et stort problem i mindre, nemmere opgaver. Du ser på, hvad chippen skal gøre, og vælger den bedste måde at organisere dens dele på.

Du kan vælge mellem flere arkitektoniske stilarterHver stil har sine egne styrker. Nogle stilarter lader dig lave en chip fra bunden. Andre bruger færdiglavede dele for at spare tid. Her er en tabel, der viser nogle almindelige stilarter og hvad der gør dem specielle:

Arkitektonisk stil | Beskrivelse |

|---|---|

Fuldt brugerdefineret design | Du bygger hele chippen fra bunden. Dette giver dig den bedste hastighed og strømudnyttelse, men det kræver meget tid og færdigheder. |

Semi-tilpasset design | Du bruger nogle færdiglavede dele og nogle specialfremstillede dele. Dette sparer tid og giver stadig gode resultater. |

Programmerbare logiske enheder (PLD) | Du kan ændre, hvordan chippen fungerer, efter du har lavet den. Dette er fantastisk til hurtigt at teste idéer. |

System-on-chip (SoC) design | Man sætter mange dele på én chip. Dette gør chippen lille og hurtig. Det ses i telefoner og smarte enheder. |

Standarddesign | Du bruger dele, der allerede er testet og klar til brug. Dette er hurtigt og fungerer godt til mange produkter. |

Tip: Vælg en arkitektur, der matcher dit projekts behov. Tænk over hastighed, ydeevne og hvor meget tid du har.

Dit valg af arkitektur påvirker, hvor meget strøm din chip bruger, og hvor hurtigt den arbejder. Du kan bruge særlige tricks til at spare strøm og øge hastigheden. Her er nogle måder, du kan gøre dette på:

Teknik | Beskrivelse |

|---|---|

Brug komponenter med lavt strømforbrug | Vælg dele, der bruger mindre energi. Dette er en fordel, hvis din chip kører på batterier. |

Power Gating | Sluk dele af chippen, når du ikke har brug for dem. |

Dynamisk spændings- og frekvensskalering (DVFS) | Skift chippens hastighed og strømforbrug baseret på, hvad den laver. |

Duty Cycling | Tænd kun for kredsløb, når du har brug for dem. |

Minimer signalskift | Reducer hvor ofte signalerne ændres for at spare energi. |

Optimer belastningskapacitans | Reducer belastningen på udgangene for at bruge mindre strøm. |

Multi-tærskel CMOS (MTCMOS) | Brug forskellige typer afbrydere for at spare strøm i nøgleområder. |

Power-Aware Synthesis | Indstil dine værktøjer til at fokusere på at spare strøm, når du bygger chippen. |

Urstyring hos RTL | Stop uret i ubrugte dele for at reducere spild af energi. |

Kropsbias | Skift spændingen for at mindske lækager og spare strøm. |

Hierarkiske magtdomæner | Opdel chippen i zoner for bedre at styre strømmen. |

Brug af FinFET-teknologi | Brug specielle transistorer, der lækker mindre og fungerer godt ved lav effekt. |

Blokdiagram

Du tegner et blokdiagram for at vise, hvordan din chip fungerer. Dette diagram bruger simple figurer til at vise hver del af chippen. Du forbinder disse figurer med linjer for at vise, hvordan data bevæger sig. Et godt blokdiagram hjælper alle med at forstå chippens plan.

Når du laver et blokdiagram, skal du:

Vis alle chippens hoveddele.

Tegn klare linjer for dataflowet.

Mærk hver blok med dens opgave.

Hold diagrammet enkelt og letlæseligt.

Et tydeligt blokdiagram hjælper dig med at opdage problemer tidligt. Det hjælper også dit team med at tale om chippen og foretage ændringer, før I begynder at bygge.

RTL-design

RTL-designfasen er, hvor du omdanner dine ideer til kode, der beskriver, hvordan din chip fungerer. Du bruger et sprog som Verilog eller VHDL til at skrive denne kode. Du fokuserer på, hvordan data bevæger sig, og hvordan hver del af chippen opfører sig. Denne fase er vigtig, fordi den sætter reglerne for, hvordan din chip vil fungere.

RTL-kodning

Du starter RTL-design ved at skrive kode, der viser, hvad hver blok gør. Du behøver ikke bekymre dig om det fysiske layout endnu. Du beskriver logikken og hvordan signaler flyder. Du bruger simple sætninger til at vise, hvordan chippen skal reagere på input. Du sørger for, at hver del fungerer sammen som planlagt.

Tip: Skriv klar og enkel kode. Brug kommentarer til at forklare vanskelige dele. Dette hjælper dig og dit team med at forstå designet senere.

Du står over for adskillige udfordringer under RTL-design. Her er en tabel, der viser de mest almindelige:

Udfordring | Beskrivelse |

|---|---|

Designkompleksitet | Du skal håndtere store designs. Flere dele betyder større risiko for fejl og længere arbejdstider. |

Sikring af designkorrekthed | Du skal kontrollere, at din kode stemmer overens med det, du vil have chippen til at gøre. |

Håndtering af strømforbrug | Du leder efter måder at spare energi på, samtidig med at chippen forbliver i god stand. |

Du skal være opmærksom på disse udfordringer. Hvis du ikke gør det, kan du ende med fejl eller en chip, der bruger for meget strøm.

Funktionel verifikation

Når du er færdig med RTL-kodningen, går du videre til designverifikation. Du tester din kode for at sikre, at den fungerer som forventet. Du bruger testbænke og simuleringsværktøjer. Du kontrollerer alle dele af RTL-designet for at finde fejl, før du bygger chippen.

Du kører mange tests for at se, om chippen reagerer korrekt. Du leder efter fejl og retter dem tidligt. Designverifikation hjælper dig med at undgå dyre fejl senere. Du gentager denne proces, indtil du føler dig sikker på, at dit RTL-design matcher dine mål.

Bemærk: God designverifikation sparer tid og penge. Du opdager problemer, før de bliver til større problemer.

Du skal huske, at RTL-design er et vigtigt trin i at lave en pålidelig chip. Omhyggelig kodning og stærk designverifikation hjælper dig med at bygge en chip, der fungerer godt og opfylder dine behov.

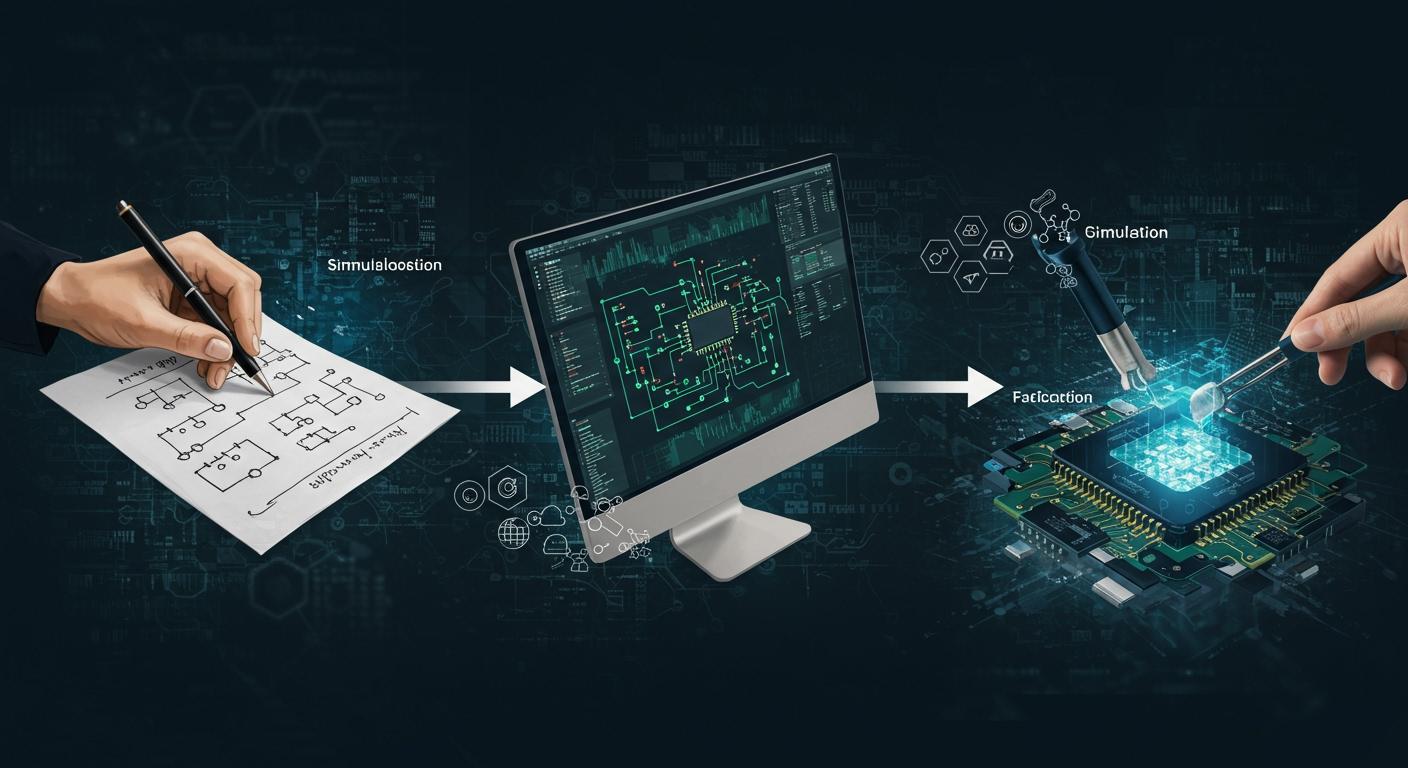

Oversigt over VLSI-designflow

Når du begynder at lære om VLSI-designcyklussen, vil du se, at VLSI-designflow giver dig en klar vej fra en idé til en fungerende chip. Dette flow hjælper dig med at undgå fejl og sikrer, at dit chipdesign fungerer som planlagt.

Faser i VLSI-designflow

Du vil følge et sæt trin i VLSI-designflowet. Hvert trin bygger videre på det sidste. Her er den sædvanlige rækkefølge, du vil se i flowet:

Konceptualisering og specifikation

Arkitektonisk design

Logikdesign

RTL-syntese

Netliste og plantegning

Placering og routing

Fysisk verifikation

Timinganalyse

Ekstraktion og simulering

Tapeout

Vigtigste aktiviteter

Du vil bemærke, at hvert trin i flowet har en særlig opgave. VLSI-designflowet starter med en klar plan og slutter med en rigtig chip. Du kontrollerer dit arbejde i hvert trin. Dette hjælper dig med at finde problemer tidligt. Du kan løse dem, før de vokser. Processen omfatter trin som specifikation, designindtastning, syntese, verifikation, layout og fabrikation. Hver af dem hjælper dig med at sikre, at dit chipdesign er korrekt. Denne omhyggelige cyklus holder fejl lave og kvaliteten høj.

Du vil se, at flowet er din guide for ethvert VLSI-projekt. Ved at følge flowet gør du dit chipdesign stærkt og pålideligt. Flowet er rygraden i enhver succesfuld VLSI-chip.

Logisk syntese

RTL til Gates

Logisk syntese er et vigtigt trin i at omdanne dine ideer til reel hardware. I denne fase tager du din RTL-kode og konverterer den til logiske gates. Du bruger specialværktøjer til at udføre dette arbejde. Disse værktøjer læser din RTL-kode og opretter et netværk af gates, der kan bygges på en chip.

Du vil se tre hovedtrin i logisk syntese:

Oversættelse: Værktøjet ændrer din RTL-kode til en form, der bruger boolske ligninger. Dette trin afhænger ikke af chipteknologien.

Optimering: Værktøjet forenkler de boolske ligninger. Det bruger metoder som summen af produkter til at gøre dette.

Teknologikortlægning: Værktøjet matcher de optimerede ligninger med rigtige porte fra et bibliotek. Det vælger porte, der passer til dine designbehov.

Tip: Tjek altid din RTL-kode for fejl, før du starter syntese. Ren kode hjælper dig med at få bedre resultater.

Optimering

Optimering hjælper dig med at finde den bedste chip til dine behov. Du ønsker, at din chip skal være lille, hurtig og bruge lidt strøm. Logiske synteseværktøjer hjælper dig med at nå disse mål ved at træffe smarte valg undervejs.

Her er en tabel, der viser, hvordan optimering påvirker din chip:

Aspect | Indvirkning på VLSI-chips |

|---|---|

Områdeoptimering | Reducerer det fysiske fodaftryk, hvilket giver flere chips på en wafer, hvilket fører til højere udbytte og lavere omkostninger. |

Hurtigoptimering | Hurtigere netværk resulterer ofte i større arealforbrug, hvilket nødvendiggør afvejninger mellem hastighed og areal. |

Energiforbrug | Større gates øger kapacitansen, hvilket fører til højere energiforbrug under kobling. |

Du skal finde balance mellem areal, hastighed og energiforbrug. Hvis du gør din chip hurtigere, kan den blive større og bruge mere strøm. Hvis du gør den mindre, kan den køre langsommere. God logisk syntese hjælper dig med at finde den bedste balance.

Arealoptimering giver dig plads til flere chips på en wafer. Dette sænker omkostningerne og giver dig mulighed for at tilføje flere funktioner.

Hastighedsoptimering får din chip til at arbejde hurtigere, men den kan bruge mere plads og energi.

Effektiv udnyttelse af plads er vigtig for at tilføje nye funktioner uden at det går ud over ydeevnen.

Du bruger logisk syntese i alle VLSI-projekter. Det former dit design og hjælper dig med at bygge chips, der fungerer godt i den virkelige verden.

Fysisk design

fysisk designfase er der, hvor du forvandler din chip's logik til et rigtigt layout. Du bestemmer, hvor hver del af chippen skal placeres, og hvordan ledninger skal forbinde dem. Dette trin er vigtigt i VLSI fysisk design, fordi det former, hvor godt din chip fungerer, og om den kan laves uden problemer.

Plantegning

Du starter den fysiske designfase med etageplanlægning. Her opdeler du chippen i blokke og giver hver blok sin egen plads. Du tænker over, hvor stor hver blok skal være, og hvor den skal placeres. God etageplanlægning hjælper dig med at undgå overfyldte områder og sikrer, at signaler bevæger sig hurtigt. Du planlægger også plads til strøm- og urledninger. Dette trin sætter strukturen for resten af VLSI's fysiske designproces.

Mange værktøjer hjælper dig med plantegning og andre opgaver i denne fase. Nogle af de mest populære værktøjer inkluderer:

Synopsys IC Compiler II: Hurtig placering og rute, strømbevidst design.

Mentor Graphics Caliber: Kontrollerer regler og matcher layout med skematisk diagram.

ANSYS RedHawk: Kontrollerer strøm og pålidelighed.

Tanner Tools: God til analog og mixed-signal layout.

Avanti Hercules: Kontrollerer signal- og strømforsyningens integritet.

OpenROAD: Open source-værktøj til fysisk design.

KLATencor L-Edit: Bruges til brugerdefineret IC-layout.

Tip: Vælg et værktøj, der passer til dit projekts behov og dit teams færdigheder.

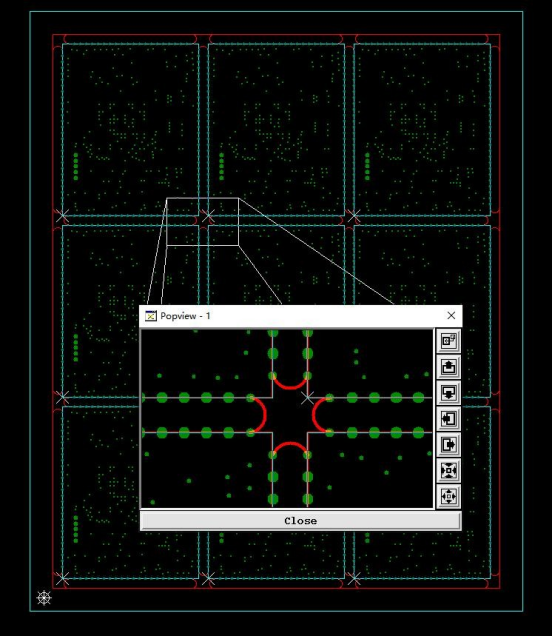

Placering og routing

Efter plantegningen går du videre til placering og routing. Du placerer hver celle eller blok på sin plads. Du ønsker at holde relaterede blokke tæt sammen. Dette hjælper signaler med at bevæge sig hurtigere og sparer strøm. Du sørger også for, at chippen ikke bliver for varm.

Dernæst trækker du ledningerne. Du tegner stier, som signaler kan bevæge sig mellem blokke. Du afbalancerer hastigheden og undgår overfyldte stier. Du kontrollerer også, at dit layout følger reglerne for fremstilling af chips. Disse trin hjælper din chip med at fungere godt og gør den nemmere at fremstille.

Du følger disse hovedtrin i den fysiske designfase:

Partitionér og planlæg chippen.

Placer celler og blokke.

Byg urtræet.

Før ledningerne.

Tjek regler og fremstillingsevne.

Optimer effekten.

Når du er færdig med den fysiske designfase, har du et layout klar til fremstilling. Dette trin er nøgle til ethvert VLSI-projekt.

Design til testbarhed

Når du arbejder på en VLSI-chip, vil du gerne sikre dig, at du nemt kan teste den. Design til testbarhed hjælper dig med at finde problemer tidligt og reparere dem, før chippen når kunderne. Du tilføjer specialfunktioner til din chip, så du kan kontrollere, om alt fungerer som planlagt. Disse funktioner gør testning hurtigere og hjælper dig med at spare penge under produktionen.

Test funktioner

Du bruger adskillige teknikker til at forbedre testbarheden i din chip. Disse metoder hjælper dig med at opdage fejl og sikre, at din chip fungerer godt.

Scanningsdesignet giver dig mulighed for at styre og kontrollere flip-flops inde i din chip under test.

Grænsescanning hjælper dig med at teste forbindelser mellem chips på et printkort uden at bruge sonder.

Indbygget selvtest (BIST) tilføjer testhardware inde i chippen, så den kan teste sig selv.

Memory BIST (MBIST) kontrollerer hukommelsesblokkene inde i din chip.

ATPG (Automatic Test Pattern Generation) opretter mønstre, der hjælper dig med at finde fejl efter fremstilling.

Disse funktioner øger testdækningen og reducerer den tid, der er nødvendig for testning. Du kan hurtigt finde fejl og undgå at sende dårlige chips til kunder.

Tip: Tilføj testfunktioner tidligt i din designproces. Dette gør testning nemmere og sænker omkostningerne.

Du ser mange fordele, når du bruger disse teknikker. Tabellen nedenfor viser, hvordan design til testbarhed hjælper din chip:

Fordel | Beskrivelse |

|---|---|

Fejldetektion | |

Forbedring af produktionsudbytte | Du løser problemer under produktionen og får flere gode chips. |

Pålidelighed | Du sørger for, at din chip fungerer godt i lang tid. |

Du kan teste komplekse chips hurtigere og mere præcist. Du leverer chips af høj kvalitet, der fungerer som forventet.

Scan kæder

Scankæder spiller en stor rolle i test af VLSI-chips. Du forbinder flip-flops i en kæde, så du kan indstille og aflæse deres værdier under test. Denne opsætning giver dig mulighed for at kontrollere indersiden af din chip uden at skille den ad.

Du bruger scanningskæder til at finde fejl i logiske blokke. Du styrer hver flip-flop og ser, hvordan signaler bevæger sig gennem din chip. Denne metode hjælper dig med at finde problemer, som normale tests måske overser.

Ved at tilføje scanningskæder gør du din chip nemmere at teste og mere pålidelig. Du reducerer også risikoen for dyre fejl, efter din chip er blevet integreret i produkter.

Bemærk: Hvis du planlægger dine scanningskæder godt, kan du spare tid og forbedre kvaliteten af din chip.

Tidlig integration af design til testbarhed hjælper dig med at reducere testtiden og undgå dyre fejl. Du bygger chips, der holder længere og yder bedre.

Timinganalyse

Timinganalyse hjælper dig med at sikre, at din chip arbejder med den rigtige hastighed. Du bruger dette trin til at kontrollere, om signaler bevæger sig hurtigt nok gennem din chip. Hvis du springer timinganalysen over, fungerer din chip muligvis ikke som planlagt. I VLSI er timinganalyse en af de vigtigste kontroller, før du afslutter dit design.

Statisk timing

Du bruger statisk timinganalyse (STA) at kontrollere timingen af din chip uden at køre testmønstre. STA ser på hver sti i dit kredsløb og kontrollerer, om signaler ankommer til tiden. Denne metode hjælper dig med at finde problemer tidligt. Du behøver ikke at bruge inputvektorer, så du kan hurtigt kontrollere alle mulige stier.

Her er nogle almindelige metoder til tidsanalyse du kan bruge:

Statisk tidsanalyse (STA)

Dynamisk tidsanalyse (DTA)

Statistisk statisk tidsanalyse (SSTA)

Analyse af godkendelsestidspunktet

Multi-corner og multi-mode (MCMM) analyse

Analyse af variation på chippen (OCV)

STA spiller en stor rolle i at forhindre timingbrud. Du ønsker, at signaler når flip-flops og registre på det rigtige tidspunkt. Hvis signaler ankommer for sent eller for tidligt, kan din chip svigte. Over 80% af designfejl i silicium sker på grund af tidsfejl. STA hjælper dig med at undgå disse dyre fejl.

Bemærk: Statisk timinganalyse kontrollerer chippens maksimale hastighed og sørger for, at alle signaler ankommer til tiden. Dette trin er afgørende for en fungerende chip.

Timing af lukning

Timing closure er den proces, hvor du løser alle timingproblemer i din chip. Du ønsker, at hvert signal skal opfylde sit timingmål. Du skal muligvis ændre dit design, flytte blokke eller justere ledningslængder. Timing closure kan kræve en stor indsats, men det er nøglen til en fungerende chip.

Du følger disse trin for at nå tidslukningen:

Analyser tidsrapporter fra STA.

Find stier, der ikke timingen giver.

Rediger dit design for at rette disse stier.

Kør STA igen for at kontrollere, om du har løst problemerne.

Gentag indtil du når tidspunktets afslutning.

Du kan bruge specialværktøjer til at hjælpe med timinglukning. Disse værktøjer viser dig, hvilke stier der skal arbejdes på. Du kan ændre dit design og se resultater hurtigt. Timinglukning sikrer, at din chip fungerer med den ønskede hastighed.

Tip: Start med at arbejde med timinglukning tidligt. Løsning timingproblemer i sidste ende kan være meget svært.

Du skal have en timing-afslutning, før du kan færdiggøre dit VLSI-design. Dette trin giver dig tillid til, at din chip vil fungere i virkeligheden.

Fysisk verifikation

Fysiske verifikationskontroller hvis din chip's layout er klar til fremstilling. Du vil være sikker på, at din chip fungerer og følger alle støberiets regler. Dette trin hjælper dig med at finde fejl, før du fremstiller chippen. Du bruger forskellige kontroller for at se, om dit layout er sikkert og korrekt.

Her er en tabel, der viser de vigtigste trin i fysisk verifikation og hvad de laver:

Verifikationstrin | Formål |

|---|---|

Design Rule Check (DRC) | Kontrollerer om layoutet følger støberiets regler for bredde og afstand. |

Layout vs. skematisk (LVS) | Sørger for, at layoutet stemmer overens med kredsløbsplanen eller skemaet. |

Elektrisk regeltjek (ERC) | Finder elektriske problemer som manglende ledninger eller for meget kapacitans. |

DRC

Du starter med Design Rule Check, kaldet DRC. Denne kontrol ser på din chip's layout og sammenligner det med støberiets regler. Disse regler angiver, hvor brede ledninger skal være, og hvor langt fra hinanden de skal være. Hvis du bryder disse regler, fungerer din chip muligvis ikke, eller den kan være svær at fremstille.

DRC er en del af den fysiske verifikationDet hjælper dig med at finde problemer som ledninger, der er for tæt på hinanden, eller former, der er for små. Ved at løse disse problemer bliver din chip nemmere at bygge og mere pålidelig.

Proces | Fokus | Formål |

|---|---|---|

DRC | Fysisk verifikation | Sørger for, at chippen kan fremstilles ved at følge designreglerne. |

Tip: Kør altid DRC, før du færdiggør dit layout. Dette trin sparer tid og penge.

LVS

Efter DRC udfører du Layout vs. Schematic, eller LVS. Denne kontrol sikrer, at dit layout matcher din kredsløbsplan. Du ønsker, at alle ledninger og dele i dit layout matcher dit skema.

LVS handler om elektrisk verifikation. Det kontrollerer, om din chip fungerer som planlagt. Hvis LVS finder noget galt, skal du rette det, før du går videre.

Proces | Fokus | Formål |

|---|---|---|

LVS | Elektrisk verifikation | Sørger for, at layoutet stemmer overens med skematisk tegning for at sikre korrekt arbejde. |

Fysisk verifikation er en vigtig del af VLSI-processen. Når du bruger DRC og LVS, sikrer du dig, at dit design er korrekt og klar til næste trin.

Fabrication

Når du er færdig med tapeout i VLSI-designcyklussen, starter du fabrikationDette trin gør dit chipdesign til virkelighed. Dine ideer bliver til siliciumchips. Disse chips bruges i telefoner, computere og andre enheder.

Wafer behandling

Waferbehandling er den første del af fremstillingen af chips. Du bruger et tyndt stykke silicium kaldet en wafer. Du følger mange trin for at bygge lag og kredsløb på det. Hvert trin tilføjer noget vigtigt til din chip.

Her er de vigtigste trin i waferbehandlingen:

Overfladerensning

Du rengør waferen for at fjerne støv.Indledende oxidation

Du dyrker et tyndt oxidlag på waferen.CVD-aflejring

Man lægger nye materialer på waferen med speciel gas.Belægning af fotoresist

Du dækker waferen med et materiale, der reagerer på lys.Metallisering og sammenkobling

Du tilføjer metal for at forbinde dele af chippen.Kemisk mekanisk polering (CMP)

Du polerer waferen for at gøre den flad og glat.Afsluttende test og pakning

Du tester chippen og gør den klar til sin emballage.

Du kan gentage nogle trin for at lave komplekse chips. Hvert trin hjælper dig med at bygge en chip, der matcher din plan.

Tip: Omhyggelig waferbehandling forhindrer defekter og producerer bedre chips.

Støberitrapper

Efter waferforarbejdning sender du din chip til et støberi til tapeout. Hvert støberi bruger sine egne metoder til at fremstille chips. De har forskellige forretningsstile, teknologier og forskningsmål.

Her er en tabel, der viser, hvad de største producenter gør:

Fabrikant | Forretningsmodel | Fokus på procesnode | FoU-fokus |

|---|---|---|---|

TSMC | Rent-leg støberi | Mindre procesnoder | Forbedring af procesnoder og forbedring af udbyttet |

Intel | Vertikal integration | Får teknologisk førende stilling tilbage | Ny emballage, AI-chips, kvanteberegning |

Samsung | Støberi og hukommelseschip | Avancerede noder | Nye ideer inden for hukommelse og logikchips |

Du vælger et støberi, der passer til dine behov. Nogle støberier fremstiller mindre og hurtigere chips. Andre arbejder på ny emballage eller specialfunktioner. Dit tapeout-trin afhænger af, hvad støberiet er bedst til.

Fremstilling er en meget vigtig del af VLSI-designcyklussen. Du skal følge hvert trin for at få gode spåner efter tapeout.

Testning og emballering

Elektrisk test

Du skal kontrollere hver chip, før den forlader fabrikken. Elektrisk testning sikrer, at din chip fungerer som planlagt. Dette trin hjælper dig med at finde problemer under fremstillingen af chippen. Du bruger forskellige måder at teste chips på. Nogle almindelige metoder er:

Fejlmodellering

Automatisk generering af testmønstre (ATPG)

Grænsescanningstest (JTAG)

Funktionel test

Parametrisk testning

DFT giver dig mulighed for at tilføje specialfunktioner, når du designer chippen. Disse funktioner gør testning enkel. Indbygget selvtest (BIST) lader chippen teste sig selv. Du behøver ikke ekstra værktøjer til dette. ATPG laver testmønstre for hurtigt at finde fejl. Disse metoder hjælper dig med at spare penge og tid. Du kan løse problemer, før kunderne får chippen. God testning betyder, at kun fungerende chips går til brugerne. Dette holder folk glade.

Tip: Elektrisk testning hjælper dig med at finde defekter tidligt. Det sikrer, at din VLSI-chip fungerer korrekt.

Emballagemetoder

Efter testen skal du beskytte din chip og tilslutte den. Emballagen gør dette for dig. Måden du pakker en chip på påvirker, hvor godt den fungerer. Den påvirker også, hvor længe den holder. Du skal tænke på varme, strøm og signaler.

Sammenkoblingsteknologi er vigtig inden for emballage. Mikrobump, gennemgående siliciumvias (TSV'er) og omfordelingslag (RDL'er) hjælper med at forbinde chippen. Mikrobump er gode til chip-til-substrat-forbindelser. Men de kan have problemer med varme og rystelser. Elektromigration og termisk migration kan skade pålideligheden.

TSV'er lader signaler og varme bevæge sig op og ned i chippen. Dette hjælper chippen med at fungere bedre. Men forskellige materialer kan revne eller gå i stykker, når chippen bliver varm eller kold.

For at forbedre emballage skal man studere varme, elektricitet og kraft. Brug af nye materialer som højdensitetsforbindelser og avancerede termiske materialer hjælper med at kontrollere varmen. Det får også chippen til at holde længere. Efterhånden som chips bliver hurtigere og mindre, betyder godt emballagedesign mere og mere.

Det kan du se testning og pakning er begge vigtige. De hjælper din chip med at fungere godt og holde længe.

Siliciumvalidering

Når du er færdig med at lave en chip, skal du kontrollere, om den fungerer som planlagt. Dette trin kaldes siliciumvalidering. Du vil sikre dig, at din chip matcher det originale design og fungerer godt i virkeligheden.

Efterproduktionskontroller

Efter fremstillingen tester du de første chips, der kommer fra fabrikken. Disse chips kaldes prototyper. Du placerer dem på specielle printkort og kører mange tests. Du leder efter problemer, der ikke viste sig under tidligere kontroller. Nogle gange undslipper fejl i den første testrunde. Nu kan du finde dem, fordi chippen kører med reel systemhastighed.

Du følger en standardproces for siliciumvalidering:

Præ-siliciumverifikation bruger software til at teste din chip, før den fremstilles. Du kører testcases i en simulator. Dette trin kontrollerer, om din RTL-kode matcher specifikationen.

Post-silicium validering starter, når du har fået den rigtige chip. Du tester chippen på hardware. Du ser, hvordan den fungerer i realtid og under virkelige forhold.

Bemærk: Post-silicium validering hjælper dig med at finde problemer, der kun opstår, når chippen kører med fuld hastighed eller i et virkeligt miljø.

Slutprodukt

Når du har gennemført alle kontroller, ved du, om din chip er klar til markedet. Du ser på, hvordan chippen yder, hvor meget strøm den bruger, og om den opfylder alle dine mål. Hvis du finder problemer, kan du løse dem, før du laver flere chips.

Her er en simpel tabel, der viser forskellen mellem trin før silicium og trin efter silicium:

Trin | Når det sker | Hvad du tester på | Testhastighed |

|---|---|---|---|

Præ-siliciumverifikation | Før fremstilling | Softwaresimulator | Ikke reel systemhastighed |

Post-silicium validering | Efter fremstilling | Ægte hardware | Reel systemhastighed |

Du har brug for siliciumvalidering for at sikre, at din VLSI-chip fungerer som planlagt. Dette trin giver dig tillid til, at dit design vil lykkes i den virkelige verden.

Du gør VLSI-chipdesign mere pålideligt ved at følge hvert trin. På denne måde kan du undgå fejl og holde dit arbejde stabilt. Kendskab til VLSI-designflowet hjælper dig med at forbedre hastighed, størrelse og strømforbrug. Nye ting som f.eks. AI-drevet automatisering og 3D-integration ændrer VLSI's fremtid. Hvis du vil udvikle dig i dit job, lære nye færdigheder, få certifikater, og tal med eksperter. Cyklussen hjælper dig med at bygge bedre chips og holde dig foran inden for teknologi.

Trend | Indvirkning på halvlederteknologi |

|---|---|

AI-drevet designautomatisering | Gør chipdesign hurtigere og nemmere |

Strategier til strømoptimering | Hjælper små enheder med at fungere bedre |

3D-integrationsteknikker | Giver bedre hastigheds- og varmekontrol |

Sikkerhed først-tilgange | Beskytter chips mod hackere |

Avancerede simuleringsværktøjer | Kontrollerer design hurtigere og mere præcist |

Tjek hvad du ved, og ret svage punkter.

Tag særlige kurser.

Mød og snak med folk i felten.

Ofte stillede spørgsmål

Hvad er VLSI-designcyklussen?

Du følger VLSI-designcyklussen trin for trin for at skabe en chip. Denne cyklus hjælper dig med at planlægge, bygge og teste din chip. Hvert trin sikrer, at din chip fungerer godt og opfylder dine behov.

Hvorfor er VLSI vigtig i elektronik?

Du bruger vlsi til at få millioner af bittesmå dele på én chip. Dette gør enheder mindre, hurtigere og smartere. Telefoner, computere og biler bruger alle vlsi-chips til at fungere bedre.

Hvordan starter man et designprojekt?

Du starter med at skrive ned, hvad du ønsker, at din chip skal gøre. Du sætter klare mål og oplister funktioner. Dette hjælper dig og dit team med at holde fokus og undgå fejl.

Hvilke værktøjer hjælper med VLSI-design?

Du bruger speciel software til at tegne, test og tjek din chip. Værktøjer som Synopsys, Mentor Graphics og Cadence hjælper dig med at designe, simulere og verificere din chip, før du laver den.

Kan man rette fejl efter at have lavet en chip?

Du kan finde og rette nogle fejl under testning. Hvis du finder store problemer, kan det være nødvendigt at ændre dit design og lave en ny chip. Omhyggelig planlægning hjælper dig undgå dyre fejl.