ডিআইপি ওভারভিউ

ডিআইপি হলো একটি প্লাগ-ইন। এই প্যাকেজিং পদ্ধতি ব্যবহার করে তৈরি চিপে দুটি সারি পিন থাকে, যা সরাসরি ডিআইপি কাঠামোযুক্ত চিপ সকেটে অথবা একই সংখ্যক সোল্ডার হোল সহ সোল্ডারিং পজিশনে সোল্ডার করা যায়। এর বৈশিষ্ট্য হল এটি সহজেই পিসিবি বোর্ডের ছিদ্র সোল্ডারিং উপলব্ধি করতে পারে এবং মাদারবোর্ডের সাথে ভালো সামঞ্জস্যপূর্ণ। তবে, এর বৃহৎ প্যাকেজিং এলাকা এবং বেধের কারণে এবং প্লাগ-ইন এবং আনপ্লাগ প্রক্রিয়ার সময় পিনগুলি সহজেই ক্ষতিগ্রস্ত হয়, তাই নির্ভরযোগ্যতা কম।

DIP হল সবচেয়ে জনপ্রিয় প্লাগ-ইন প্যাকেজ, এবং এর প্রয়োগ পরিসরে স্ট্যান্ডার্ড লজিক আইসি, মেমরি LSI, মাইক্রোকম্পিউটার সার্কিট ইত্যাদি অন্তর্ভুক্ত রয়েছে। ছোট আউটলাইন প্যাকেজ (SOP)। প্রাপ্ত SOJ (J-টাইপ পিন ছোট আউটলাইন প্যাকেজ), TSOP (পাতলা ছোট আউটলাইন প্যাকেজ), VSOP (খুব ছোট আউটলাইন প্যাকেজ), SSOP (সঙ্কুচিত SOP), TSSOP (পাতলা সঙ্কুচিত SOP) এবং SOT (ছোট আউটলাইন ট্রানজিস্টর), SOIC (ছোট আউটলাইন ইন্টিগ্রেটেড সার্কিট) ইত্যাদি।

ডিআইপি ডিভাইস অ্যাসেম্বলি ডিজাইনের ত্রুটি

1. বড় পিসিবি প্যাকেজ গর্ত

পিসিবির প্লাগ-ইন হোল এবং প্যাকেজ পিন হোল স্পেসিফিকেশন বই অনুসারে আঁকা হয়। প্লেট তৈরির প্রক্রিয়া চলাকালীন, গর্তটি তামার প্রলেপযুক্ত হতে হবে এবং সাধারণ সহনশীলতা প্লাস বা মাইনাস 0.075 মিমি। যদি পিসিবি প্যাকেজ হোলটি ভৌত ডিভাইসের পিনের চেয়ে বড় হয়, তাহলে এটি ডিভাইসটি আলগা হয়ে যাবে, অপর্যাপ্ত টিনিং, খালি সোল্ডারিং এবং অন্যান্য মানের সমস্যা সৃষ্টি করবে।

নিচের চিত্রটি দেখুন: WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) এর ডিভাইস পিনটি 1.3 মিমি এবং PCB প্যাকেজ হোলটি 1.6 মিমি। ওয়েভ সোল্ডারিংয়ের সময় বড় গর্তের ব্যাস খালি সোল্ডারিংয়ের দিকে নিয়ে যায়।

উপরের চিত্র থেকে অব্যাহত রেখে, ডিজাইনের প্রয়োজনীয়তা অনুসারে WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) উপাদানগুলি কিনুন এবং পিন 1.3 মিমি সঠিক।

2. ছোট পিসিবি প্যাকেজ গর্ত

- পিসিবি বোর্ডের প্লাগ-ইন কম্পোনেন্টের সোল্ডার প্যাডে গর্তটি ছোট, এবং কম্পোনেন্টটি ঢোকানো যাবে না। এই সমস্যার একমাত্র সমাধান হল গর্তের ব্যাস বড় করা এবং তারপর প্লাগটি ঢোকানো, তবে গর্তে কোনও তামা থাকবে না। এই পদ্ধতিটি ব্যবহার করা যেতে পারে যদি এটি একটি একক-পার্শ্বযুক্ত বা দ্বি-পার্শ্বযুক্ত বোর্ড হয়। একক-পার্শ্বযুক্ত বা দ্বি-পার্শ্বযুক্ত বোর্ডের বাইরের স্তরটি বৈদ্যুতিকভাবে পরিবাহী, এবং সোল্ডারিংয়ের পরে এটি পরিবাহী হতে পারে। যদি মাল্টি-লেয়ার বোর্ডের প্লাগ-ইন গর্তটি ছোট হয় এবং অভ্যন্তরীণ স্তরটি বৈদ্যুতিকভাবে পরিবাহী হয়, তবে পিসিবি বোর্ডটি কেবল পুনরায় করা যেতে পারে, কারণ গর্তটি প্রসারিত করে অভ্যন্তরীণ স্তর পরিবাহী প্রতিকার করা যায় না।

নিচের চিত্রটি দেখুন: নকশার প্রয়োজনীয়তা অনুসারে, A2541Hwv-3P_A2541HWV-3P(CJT) এর উপাদানগুলি কেনা হয়েছে। পিনটি 1.0 মিমি, এবং PCB প্যাকেজ প্যাডের গর্তটি 0.7 মিমি, যার ফলে এটি ঢোকানো অসম্ভব।

উপরের চিত্র থেকে অব্যাহত রেখে, নকশার প্রয়োজনীয়তা অনুসারে, A2541Hwv-3P_A2541HWV-3P(CJT) এর উপাদানগুলি কেনা হয়েছে। পিন 1.0 মিমি সঠিক।

৩. পিসিবি প্যাকেজ পিনের মধ্যে দূরত্ব উপাদানগুলির সাথে মেলে না

ডিআইপি ডিভাইসের পিসিবি প্যাকেজ প্যাডগুলির কেবল পিনের মতো একই গর্তের ব্যাসই নয়, পিনের মধ্যে ব্যবধানও একই দূরত্ব হতে হবে।

পিন হোল স্পেসিং এবং ডিভাইসের মধ্যে অসঙ্গতির কারণে ডিভাইসটি ঢোকানো যাবে না, সামঞ্জস্যযোগ্য পিন স্পেসিং সহ উপাদানগুলি ছাড়া।

নিচের চিত্রটি দেখুন: PCB প্যাকেজের পিন হোলের ব্যবধান ৭.৬ মিমি, এবং ক্রয়কৃত উপাদানের পিন হোলের ব্যবধান ৫.০ মিমি। ২.৬ মিমি পার্থক্য ডিভাইসটিকে ব্যবহারের অযোগ্য করে তোলে।

৪. পিসিবি প্যাকেজের গর্তের ব্যবধান খুব কাছাকাছি, যার ফলে টিনের শর্ট সার্কিট হয়।

প্যাকেজ ডিজাইন এবং অঙ্কন করার সময়, আপনাকে পিনের গর্তগুলির মধ্যে দূরত্বের দিকে মনোযোগ দিতে হবে। এমনকি যদি ছোট পিনের গর্তের ব্যবধান দিয়ে খালি বোর্ড তৈরি করা যায়, তবে সমাবেশের সময় ওয়েভ সোল্ডারিংয়ের সময় টিনের শর্ট সার্কিট হওয়া সহজ।

নিচের চিত্রটি দেখুন: টিনের শর্ট সার্কিট পিনের দূরত্ব কম থাকার কারণে হতে পারে। ওয়েভ সোল্ডারিং টিনের শর্ট সার্কিটের অনেক কারণ রয়েছে। যদি ডিজাইনের প্রান্তটি আগে থেকে অ্যাসেম্বলিবিলিটি রোধ করতে পারে, তাহলে সমস্যার সংঘটনের হার কমানো যেতে পারে।

একটি ডিআইপি ডিভাইসের পিনে অপর্যাপ্ত টিনের একটি বাস্তব ঘটনা

উপাদানের মূল আকার এবং PCB প্যাড গর্তের আকারের মধ্যে অমিলের সমস্যা

সমস্যা বর্ণনা: একটি পণ্য ডিআইপি তরঙ্গায়িত করার পর, দেখা গেল যে নেটওয়ার্ক সকেটের স্থির ফুট প্যাডে টিনটি গুরুতরভাবে অপর্যাপ্ত ছিল, যা একটি ফাঁকা সোল্ডারিং ছিল।

সমস্যার প্রভাব: নেটওয়ার্ক সকেট এবং পিসিবি বোর্ডের স্থায়িত্ব খারাপ হবে, এবং পণ্য ব্যবহারের সময় সিগন্যাল পিনের উপর চাপ পড়বে, যা অবশেষে সিগন্যাল পিনের সংযোগ বিচ্ছিন্ন করবে এবং পণ্যের কর্মক্ষমতাকে প্রভাবিত করবে। ব্যবহারকারীর ব্যবহারের সময় ব্যর্থতার ঝুঁকি রয়েছে;

সমস্যা এক্সটেনশন: নেটওয়ার্ক সকেটের স্থিতিশীলতা খারাপ, সিগন্যাল পিনের সংযোগ কর্মক্ষমতা খারাপ, এবং মানসম্মত সমস্যা রয়েছে। অতএব, এটি ব্যবহারকারীদের নিরাপত্তার ঝুঁকি তৈরি করতে পারে এবং চূড়ান্ত ক্ষতি অকল্পনীয়।

wonderfulpcb ডিএফএম সার্ভিসেস সমাবেশ বিশ্লেষণ ডিভাইস পিন পরীক্ষা করে

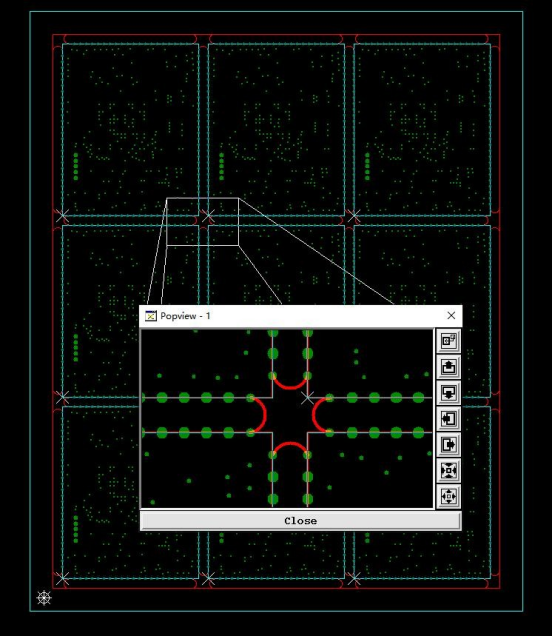

wonderfulpcb DFM Services অ্যাসেম্বলি বিশ্লেষণ ফাংশনে DIP ডিভাইসের পিনের একটি বিশেষ পরিদর্শন রয়েছে। পরিদর্শন আইটেমগুলির মধ্যে রয়েছে থ্রু হোলের পিনের সংখ্যা, THT পিনের সীমা, THT পিনের সীমা এবং THT পিনের বৈশিষ্ট্য। পিনের পরিদর্শন আইটেমগুলি মূলত DIP ডিভাইসের পিন ডিজাইনের সম্ভাব্য সমস্যাগুলি কভার করে।

নকশা সম্পন্ন হওয়ার পর, পণ্য উৎপাদনের আগে আগে থেকেই নকশার ত্রুটিগুলি আবিষ্কার করতে এবং নকশার অসঙ্গতিগুলি সমাধান করতে wonderfulpcb DFM Services অ্যাসেম্বলি বিশ্লেষণ ব্যবহার করুন। এটি সমাবেশ প্রক্রিয়ার সময় নকশার সমস্যা, উৎপাদন সময় বিলম্ব এবং গবেষণা ও উন্নয়ন খরচ নষ্ট করা এড়াতে পারে।