Вы можете спросить, что такое цикл проектирования СБИС. Этот процесс позволяет шаг за шагом создавать работающую микросхему. В сверхбольшой интеграции используется полупроводниковая технология. Это позволяет разместить миллионы транзисторов на одном кристалле. Каждый этап цикла важен. Пропуск одного из этапов может привести к ошибкам или неработоспособности микросхемы. Сфера СБИС развивалась очень быстро. Мировой рынок стоил около… 634.85 млрд долларов США в 2025 годуК 2034 году он может достичь 1 055,39 млрд долларов США. Обычно цикл состоит из следующих основных этапов:

Сбор требований

Проектирование на системном уровне

RTL-дизайн

Функциональная проверка

Синтез

Место и маршрут

Физическая проверка

Полупроводниковые технологии влияют на электронику, которой вы пользуетесь каждый день.

Характеристики

Этап спецификации — первый этап цикла проектирования СБИС. Здесь вы решаете, что должна делать микросхема. Вы также решаете, насколько хорошо она должна работать. Этот этап поможет вам сделать правильный выбор в дальнейшем. Если вы выполните его правильно, ваша микросхема, скорее всего, будет работать. Вы также сможете избежать серьёзных ошибок и сэкономить время.

Требования

Вы должны иметь четкие требования Прежде чем приступить к проектированию микросхемы СБИС. Эти требования определяют, что должна делать микросхема. Они также определяют её скорость, мощность и размер. Вы перечисляете все функции, необходимые микросхеме. Составление этих требований помогает всем понять цели. Это гарантирует, что проект соответствует потребностям пользователей.

Совет: формулируйте требования простыми словами. Используйте короткие предложения. Старайтесь не использовать сложные слова.

Многие команды используют разные способы организации своих требований. Вот таблица с некоторыми распространёнными методами:

Методология | Описание |

|---|---|

Система Верилог | Имеет множество инструментов для проверки работоспособности чипа. Использует объектно-ориентированное программирование и случайное тестирование. |

Универсальная методология проверки (UVM) | Использует SystemVerilog. Он помогает командам создавать тесты, которые можно использовать повторно. |

VHDL | Часто используется для разработки и проверки проектов микросхем. Помогает моделировать и тестировать оборудование. |

е (Specman) | Имеет мощные инструменты для проверки чипов. Использует случайное тестирование по правилам. |

C/C++ и Python | Используется для изготовления тестовых систем и испытательных стендов. |

Системные цели

Ты устанавливаешь системные цели для помощи в проектировании. Эти цели включают в себя определение скорости работы чипа, его стоимости и потребляемой мощности. Вы решаете, как чип будет работать с другими устройствами. Вы также планируете будущие изменения. Постановка целей помогает команде не сбиться с пути.

Этап спецификации очень важен при проектировании микросхем СБИС. Она задаёт основу для всего процесса. Хорошая спецификация гарантирует, что чип будет работать так, как ему положено. Это ключ к успеху проекта.

Архитектура

Проектирование системы

Вы начинаете фаза архитектуры Планируя работу чипа, вы решаете, что будет делать каждая его часть. Вы также выбираете, как эти части будут взаимодействовать друг с другом. Этот шаг помогает разбить большую задачу на более мелкие, более простые задачи. Вы анализируете, что должен делать чип, и выбираете наилучший способ организации его частей.

Вы можете выбрать из нескольких архитектурные стилиУ каждого стиля есть свои сильные стороны. Некоторые позволяют изготовить чип с нуля. Другие используют готовые детали для экономии времени. Вот таблица, которая показывает некоторые распространенные стили. и что делает их особенными:

Архитектурный стиль | Описание |

|---|---|

Полностью индивидуальный дизайн | Вы разрабатываете весь чип с нуля. Это обеспечивает максимальную скорость и производительность, но требует много времени и навыков. |

Полуиндивидуальный дизайн | Вы используете как готовые детали, так и изготовленные на заказ. Это экономит время и при этом даёт хорошие результаты. |

Программируемые логические устройства (PLD) | Вы можете изменить принцип работы чипа после его изготовления. Это очень удобно для быстрой проверки идей. |

Проектирование системы на кристалле (SoC) | Вы размещаете множество компонентов на одном чипе. Это делает чип компактным и быстрым. Это можно увидеть в телефонах и смартфонах. |

Готовый дизайн | Вы используете уже протестированные и готовые к использованию детали. Это быстро и подходит для многих продуктов. |

Совет: выберите архитектуру, соответствующую потребностям вашего проекта. Учитывайте скорость, производительность и количество свободного времени.

Выбор архитектуры влияет на энергопотребление и скорость работы вашего чипа. Вы можете использовать специальные приёмы для экономии энергии и повышения скорости. Вот несколько способов это сделать:

Техника | Описание |

|---|---|

Используйте маломощные компоненты | Выбирайте детали, потребляющие меньше энергии. Это полезно, если ваш чип работает от батареек. |

Мощность стробирования | Отключайте части чипа, когда они вам не нужны. |

Динамическое масштабирование напряжения и частоты (DVFS) | Измените скорость и энергопотребление чипа в зависимости от выполняемых им задач. |

Рабочий цикл | Включайте цепи только тогда, когда они вам нужны. |

Минимизировать переключение сигналов | Сократите частоту смены сигналов для экономии энергии. |

Оптимизация емкости нагрузки | Уменьшите нагрузку на выходы, чтобы потреблять меньше энергии. |

Многопороговый КМОП (MTCMOS) | Используйте различные типы выключателей для экономии электроэнергии в ключевых зонах. |

Энергоориентированный синтез | Настройте свои инструменты так, чтобы они были направлены на экономию энергии при сборке чипа. |

Синхронизация часов в RTL | Остановите часы в неиспользуемых деталях, чтобы сократить потери энергии. |

Предвзятость тела | Измените напряжение, чтобы уменьшить утечки и сэкономить электроэнергию. |

Иерархические домены власти | Разделите чип на зоны для лучшего управления мощностью. |

Использование технологии FinFET | Используйте специальные транзисторы, которые имеют меньшие утечки и хорошо работают при низкой мощности. |

Блок-схема

Вы рисуете блок-схему, чтобы показать, как работает ваш чип. Эта схема использует простые фигуры для обозначения каждой части чипа. Соединяя эти фигуры линиями, вы показываете, как передаются данные. Хорошая блок-схема помогает всем понять схему чипа.

При создании блок-схемы необходимо:

Показать все основные части микросхемы.

Нарисуйте четкие линии для потока данных.

Обозначьте каждый блок его задачей.

Сделайте диаграмму простой и удобной для чтения.

Чёткая блок-схема поможет вам выявить проблемы на ранней стадии. Она также поможет вашей команде обсудить чип и внести изменения до начала сборки.

РТЛ Дизайн

На этапе RTL-проектирования вы воплощаете свои идеи в код, описывающий работу вашего чипа. Для написания кода используется язык программирования, например, Verilog или VHDL. Вы уделяете особое внимание передаче данных и поведению каждой части чипа. Этот этап важен, поскольку он задаёт правила работы вашего чипа.

RTL-кодирование

Проектирование RTL начинается с написания кода, демонстрирующего назначение каждого блока. Физическая компоновка пока не имеет значения. Вы описываете логику и то, как проходят сигналы. Вы используете простые операторы, чтобы показать, как микросхема должна реагировать на входные сигналы. Вы обеспечиваете согласованную работу всех компонентов.

Совет: Пишите понятный и простой код. Используйте комментарии для пояснения сложных моментов. Это поможет вам и вашей команде в дальнейшем разобраться в проекте.

При проектировании RTL вы сталкиваетесь с рядом трудностей. Ниже представлена таблица, в которой представлены наиболее распространённые из них:

Вызов | Описание |

|---|---|

Сложность дизайна | Вам придётся управляться с крупными проектами. Чем больше деталей, тем выше вероятность ошибок и дольше время работы. |

Обеспечение правильности дизайна | Вам необходимо проверить, соответствует ли ваш код тому, что должен делать чип. |

Управление энергопотреблением | Вы ищете способы экономии энергии и поддержания бесперебойной работы микросхемы. |

Необходимо обращать внимание на эти проблемы. В противном случае могут возникнуть ошибки или чип будет потреблять слишком много энергии.

Функциональная проверка

После завершения RTL-кодирования вы переходите к проверке проекта. Вы тестируете код, чтобы убедиться, что он работает так, как и ожидалось. Вы используете тестовые стенды и инструменты моделирования. Вы проверяете каждую часть RTL-проекта, чтобы найти ошибки, прежде чем приступить к сборке чипа.

Вы проводите множество тестов, чтобы убедиться в корректности работы микросхемы. Вы ищете ошибки и устраняете их на ранних этапах. Проверка проекта помогает избежать дорогостоящих ошибок в будущем. Вы повторяете этот процесс, пока не будете уверены, что ваш RTL-проект соответствует вашим целям.

Примечание: Качественная проверка проекта экономит время и деньги. Вы выявляете проблемы до того, как они перерастут в серьёзные.

Важно помнить, что RTL-проектирование — ключевой этап в создании надёжного чипа. Тщательное кодирование и тщательная проверка проекта помогут вам создать чип, который будет хорошо работать и соответствовать вашим потребностям.

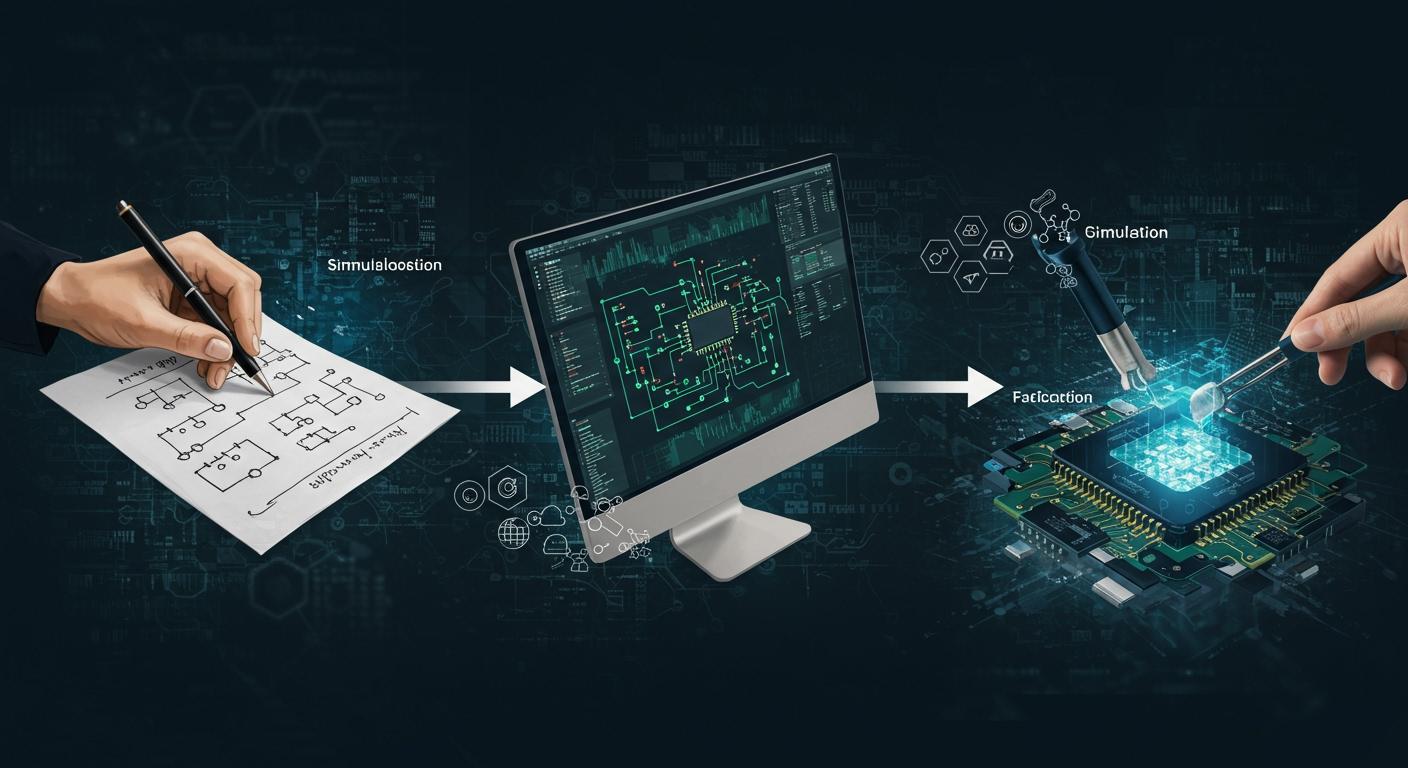

Обзор процесса проектирования СБИС

Когда вы начнете изучать цикл проектирования СБИС, вы увидите, что процесс проектирования СБИС Обеспечивает вам чёткий путь от идеи до работающего чипа. Этот процесс помогает избежать ошибок и гарантирует, что ваш чип будет работать так, как задумано.

Этапы проектирования СБИС

Вам предстоит выполнить ряд шагов в процессе проектирования СБИС. Каждый шаг основывается на предыдущем. Вот обычный порядок, который вы увидите в процессе:

Концептуализация и спецификация

Архитектурный дизайн

Логика Дизайн

Синтез RTL

Netlist и Floorplanning

Размещение и маршрутизация

Физическая проверка

Временной анализ

Извлечение и моделирование

Tapeout

Основные мероприятия

Вы заметите, что каждый этап процесса имеет свою особую задачу. Процесс проектирования СБИС начинается с чёткого плана и заканчивается реальной микросхемой. Вы проверяете свою работу на каждом этапе. Это помогает выявлять проблемы на ранних стадиях и устранять их до того, как они станут серьёзными. Поток включает такие этапы, как спецификация, ввод проекта, синтез, проверка, макет и изготовление. Каждый этап помогает вам убедиться в правильности конструкции вашего чипа. Этот тщательный цикл обеспечивает низкий уровень ошибок и высокое качество.

Вы увидите, что последовательность действий — это ваше руководство для каждого проекта СБИС. Следуя ей, вы сделаете свою микросхему прочной и надёжной. Последовательность действий — основа каждой успешной микросхемы СБИС.

Логический синтез

RTL к воротам

Логический синтез — ключевой этап в воплощении ваших идей в реальное оборудование. На этом этапе вы берёте RTL-код и преобразуете его в логические вентили. Для этого используются специальные инструменты. Эти инструменты считывают RTL-код и создают сеть вентилей, которую можно реализовать на кристалле.

Вы увидите три основных этапа логического синтеза:

Перевод: Инструмент преобразует ваш RTL-код в форму, использующую булевы уравнения. Этот шаг не зависит от технологии чипа.

Оптимизация: инструмент упрощает булевы уравнения. Для этого используются такие методы, как сумма произведений.

Картирование технологий: инструмент сопоставляет оптимизированные уравнения с реальными вентилями из библиотеки. Он выбирает вентили, соответствующие вашим проектным требованиям.

Совет: Всегда проверяйте RTL-код на наличие ошибок перед началом синтеза. Чистый код поможет добиться лучших результатов.

Оптимизация

Оптимизация поможет вам подобрать оптимальный чип для ваших нужд. Вы хотите, чтобы ваш чип был компактным, быстрым и потреблял мало энергии. Инструменты логического синтеза помогут вам достичь этих целей, делая разумный выбор в процессе.

Вот таблица, показывающая, как оптимизация влияет на ваш чип:

Аспект | Влияние на микросхемы СБИС |

|---|---|

Оптимизация площади | Уменьшает занимаемую площадь, позволяя разместить больше чипов на пластине, что приводит к повышению выхода годных изделий и снижению затрат. |

Оптимизация скорости | Более быстрые сети часто требуют большего пространства, что требует компромисса между скоростью и площадью. |

Энергопотребление | Большие затворы увеличивают емкость, что приводит к большему потреблению энергии во время переключения. |

Вам необходимо сбалансировать площадь, скорость и энергопотребление. Если вы сделаете чип быстрее, он может стать больше и потреблять больше энергии. Если вы уменьшите его, он может работать медленнее. Хороший логический синтез поможет вам найти оптимальный баланс.

Оптимизация площади позволяет разместить больше чипов на пластине. Это снижает затраты и позволяет добавлять больше функций.

Оптимизация скорости заставляет ваш чип работать быстрее, но при этом он может потреблять больше места и энергии.

Эффективное использование пространства важно для добавления новых функций без ущерба для производительности.

Логический синтез используется в каждом проекте СБИС. Он формирует вашу конструкцию и помогает создавать микросхемы, которые хорошо работают в реальных условиях.

Физический дизайн

этап физического проектирования Здесь вы превращаете логику вашего чипа в реальную схему. Вы решаете, где будет располагаться каждая часть чипа и как будут соединяться провода. Этот этап важен при проектировании физического СБИС, поскольку он определяет, насколько хорошо работает ваш чип и возможно ли его изготовление без проблем.

Планировка этажа

Этап физического проектирования начинается с планирования площади. На этом этапе кристалл делится на блоки и каждому блоку отводится своё место. Вы продумываете размер каждого блока и его расположение. Грамотное планирование площади помогает избежать скопления зон и обеспечивает быструю передачу сигналов. Вы также планируете пространство для линий питания и тактовой частоты. Этот этап задаёт структуру для остальной части процесса физического проектирования СБИС.

На этом этапе вам помогут многочисленные инструменты для планирования этажей и решения других задач. Некоторые из самых популярных инструментов включают в себя:

Synopsys IC Compiler II: быстрое размещение и маршрутизация, энергосберегающая конструкция.

Mentor Graphics Calibre: проверяет правила и сопоставляет макет со схемой.

ANSYS RedHawk: Проверяет мощность и надежность.

Tanner Tools: хорошо подходит для разводки аналоговых и смешанных сигналов.

Avanti Hercules: проверяет целостность сигнала и питания.

OpenROAD: инструмент с открытым исходным кодом для физического проектирования.

KLATencor L-Edit: используется для индивидуальной компоновки ИС.

Совет: выберите инструмент, который соответствует потребностям вашего проекта и навыкам вашей команды.

Размещение и маршрутизация

После планирования этажа переходим к размещению и маршрутизации. Каждый элемент или блок размещается на своём месте. Связанные блоки желательно размещать близко друг к другу. Это способствует более быстрой передаче сигналов и экономии энергии. Кроме того, необходимо следить за тем, чтобы чип не перегревался.

Затем вы прокладываете провода. Вы прокладываете пути передачи сигналов между блоками. Вы балансируете скорость и избегаете перегруженных путей. Вы также проверяете, соответствует ли ваша топология правилам изготовления микросхем. Эти шаги способствуют корректной работе микросхемы и упрощают её производство.

На этапе физического проектирования выполняются следующие основные шаги:

Разметьте и спланируйте чип.

Размещайте ячейки и блоки.

Постройте дерево часов.

Проложите провода.

Проверьте правила и технологичность.

Оптимизируйте мощность.

После завершения этапа физического проектирования у вас будет готовый к производству макет. Этот этап ключ для каждого проекта СБИС.

Дизайн для тестируемости

При работе с микросхемой СБИС вы хотите быть уверены в том, что ее можно будет легко протестировать. Проектирование с учетом тестируемости помогает выявлять проблемы на ранних стадиях и исправить их до того, как чип попадёт к заказчику. Вы добавляете в свой чип специальные функции, чтобы проверить, всё ли работает по плану. Эти функции ускоряют тестирование и помогают сэкономить деньги на производстве.

Особенности тестирования

Для улучшения тестируемости вашего чипа используется ряд методов. Эти методы помогают обнаружить неисправности и обеспечить его корректную работу.

Конструкция сканера позволяет вам контролировать и проверять триггеры внутри микросхемы во время тестов.

Периферийное сканирование позволяет тестировать соединения между микросхемами на плате без использования зондов.

Встроенная самодиагностика (BIST) добавляет в чип тестовое оборудование, чтобы он мог проверить себя.

Memory BIST (MBIST) проверяет блоки памяти внутри вашего чипа.

ATPG (автоматическая генерация тестовых шаблонов) создает шаблоны, которые помогают находить неисправности после производства.

Эти функции расширяют охват тестирования и сокращают время, необходимое для его проведения. Вы можете быстро обнаружить неисправности и избежать отправки некачественных чипов клиентам.

Наконечник: Добавляйте тестовые функции заранее в процессе проектирования. Это упрощает тестирование и снижает затраты.

Использование этих методов даёт множество преимуществ. В таблице ниже показано, как проектирование с учётом тестируемости помогает вашему чипу:

Польза | Описание |

|---|---|

Обнаружение неисправностей | |

Повышение производительности производства | Вы устраняете проблемы в процессе производства и получаете больше качественных чипов. |

Надежность | Вы гарантируете, что ваш чип будет исправно работать в течение длительного времени. |

Вы сможете тестировать сложные микросхемы быстрее и точнее. Вы поставляете высококачественные микросхемы, которые работают так, как и ожидалось.

Сканирование цепей

Цепи сканирования играют важную роль в тестировании микросхем СБИС. Триггеры соединяются в цепочку, чтобы можно было устанавливать и считывать их значения во время тестирования. Такая схема позволяет проверить внутреннюю часть микросхемы, не разбирая её.

Вы используете цепочки сканирования для поиска неисправностей в логических блоках. Вы контролируете каждый триггер и наблюдаете, как сигналы проходят через микросхему. Этот метод помогает обнаружить проблемы, которые обычные тесты могут пропустить.

Добавление цепей сканирования упрощает тестирование чипа и повышает его надежность. Вы также снижаете риск дорогостоящих отказов после того, как чип поступит в продажу.

Примечание: Если вы правильно спланируете цепочки сканирования, вы сможете сэкономить время и улучшить качество вашего чипа.

Интеграция дизайна для обеспечения тестируемости на ранних этапах помогает сократить время тестирования и избежать дорогостоящих ошибок. Вы создаёте чипы, которые служат дольше и работают лучше.

Временной анализ

Временной анализ помогает убедиться, что ваша микросхема работает на нужной скорости. Этот этап используется для проверки достаточной скорости прохождения сигналов через микросхему. Если пропустить временной анализ, микросхема может работать не так, как планировалось. В СБИС временной анализ — одна из важнейших проверок перед завершением проектирования.

Статическое время

Ты используешь статический временной анализ (STA) Для проверки синхронизации микросхемы без запуска тестовых шаблонов. STA проверяет каждый путь в схеме и своевременность поступления сигналов. Этот метод помогает обнаружить проблемы на ранней стадии. Вам не нужно использовать входные векторы, поэтому вы можете быстро проверить все возможные пути.

Вот некоторые общие методы временного анализа Вы можете использовать:

Статический временной анализ (STA)

Динамический временной анализ (DTA)

Статистический статический временной анализ (SSTA)

Анализ сроков подписания

Многоугловой и многомодовый анализ (MCMM)

Анализ вариаций на кристалле (OCV)

STA играет важную роль в предотвращении нарушений синхронизации. Необходимо, чтобы сигналы достигали триггеров и регистров в нужный момент. Если сигналы поступают слишком поздно или слишком рано, микросхема может выйти из строя. Более 80% неудачных проектов в кремнии происходят из-за нарушений синхронизации. STA помогает избежать этих дорогостоящих ошибок.

Примечание: Статический временной анализ проверяет максимальную скорость вашего чипа и обеспечивает своевременность поступления всех сигналов. Этот этап крайне важен для работоспособности чипа.

Время закрытия

Замыкание временных интервалов — это процесс устранения всех временных проблем в вашей микросхеме. Необходимо, чтобы каждый сигнал соответствовал заданному временному интервалу. Возможно, потребуется изменить конструкцию, переместить блоки или изменить длину проводов. Замыкание временных интервалов может потребовать значительных усилий, но это ключ к работоспособности микросхемы.

Для достижения закрытия по времени выполните следующие действия:

Анализируйте отчеты о времени от STA.

Найдите пути, не учитывающие синхронность.

Измените свой дизайн, чтобы исправить эти пути.

Запустите STA еще раз, чтобы проверить, устранены ли проблемы.

Повторяйте, пока не достигнете момента закрытия.

Для оптимизации временных интервалов можно использовать специальные инструменты. Эти инструменты покажут, какие пути требуют доработки. Вы сможете быстро изменить схему и увидеть результаты. Благодаря оптимизации временных интервалов ваш чип будет работать на нужной вам скорости.

Совет: начните работать над временем закрытия заранее. Исправление проблемы со временем в конце может быть очень тяжело.

Прежде чем завершить проектирование СБИС, необходимо замыкание временных интервалов. Этот шаг даст вам уверенность в том, что ваша микросхема будет работать в реальных условиях.

Физическая проверка

Физические проверки Если топология вашего чипа готова к производству. Вы хотите быть уверены, что чип будет работать и будет соответствовать всем правилам литейного производства. Этот шаг поможет вам обнаружить ошибки до изготовления чипа. Вы используете различные проверки, чтобы убедиться в безопасности и правильности топологии.

Вот таблица, в которой перечислены основные этапы физической проверки. и что они делают:

Шаг проверки | Цель |

|---|---|

Проверка правил проектирования (DRC) | Проверяет, соответствует ли макет правила литейного производства по ширине и интервал. |

Макет против схемы (LVS) | Убедитесь, что макет соответствует схеме или принципиальной схеме. |

Проверка правил электробезопасности (ERC) | Обнаруживает электрические проблемы, такие как отсутствующие провода или слишком большая емкость. |

DRC

Вы начинаете с проверки правил проектирования (DRC). Эта проверка проверяет топологию вашей микросхемы и сравнивает её с правилами литейного производства. Эти правила определяют ширину проводников и расстояние между ними. Нарушение этих правил может привести к неработоспособности микросхемы или вызвать трудности в её изготовлении.

DRC является частью физической проверки. Это помогает обнаружить такие проблемы, как слишком близко расположенные провода или слишком маленькие детали. Устранение этих проблем упрощает сборку микросхемы и повышает её надёжность.

Разработка | Фокус | Цель |

|---|---|---|

DRC | Физическая проверка | Обеспечивает возможность изготовления чипа в соответствии с правилами проектирования. |

Совет: Всегда запускайте DRC перед завершением макета. Это сэкономит время и деньги.

LVS

После проверки достоверности данных (DRC) выполняется проверка схемы (LVS). Эта проверка позволяет убедиться, что ваша схема соответствует схеме. Необходимо, чтобы каждый провод и деталь в схеме соответствовали схеме.

LVS — это проверка электрических характеристик. Она проверяет, будет ли ваш чип работать так, как вы планировали. Если LVS обнаружит какую-либо неисправность, необходимо её устранить, прежде чем двигаться дальше.

Разработка | Фокус | Цель |

|---|---|---|

LVS | Электрическая проверка | Убедитесь, что макет соответствует схеме для корректной работы. |

Физическая верификация — важная часть процесса разработки СБИС. Использование DRC и LVS гарантирует корректность проекта и его готовность к следующему этапу.

Изготовление дверей

После завершения цикла проектирования СБИС вы начинаете изготовлениеЭтот шаг превращает ваш проект чипа в реальность. Ваши идеи воплощаются в кремниевые чипы. Эти чипы устанавливаются в телефоны, компьютеры и другие устройства.

Обработка пластин

обработка пластин Это первый этап создания чипов. Вы используете тонкую кремниевую пластину, называемую пластиной. Создание слоёв и схем на ней происходит в несколько этапов. Каждый этап добавляет что-то важное к вашему чипу.

Вот основные этапы обработки пластин::

Очистка поверхности

Вы очищаете пластину от пыли.Начальное окисление

На пластине выращивается тонкий слой оксида.CVD-осаждение

Новые материалы наносятся на пластину с помощью специального газа.Покрытие фоторезист

Вы покрываете пластину материалом, реагирующим на свет.Металлизация и межсоединение

Для соединения частей микросхемы добавляется металл.Химико-механическая полировка (ХМП)

Вы полируете пластину, чтобы она стала плоской и гладкой.Окончательное тестирование и упаковка

Вы тестируете чип и готовите его к упаковке.

Для создания сложных чипов можно повторять некоторые этапы. Каждый этап помогает создать чип, соответствующий вашему плану.

Совет: Тщательная обработка пластин исключает появление дефектов и позволяет получать более качественные чипы.

Этапы литейного производства

После обработки пластины чип отправляется на литейный завод для монтажа. Каждый литейный завод использует свои методы производства чипов. У них разные стили ведения бизнеса, технологии и исследовательские цели.

Вот таблица, которая показывает, что делают ведущие производители:

Производитель | Бизнес-модель | Фокус на узле процесса | Фокус на НИОКР |

|---|---|---|---|

TSMC | Чисто литейное производство | Меньшие технологические узлы | Улучшение узлов процесса и повышение производительности |

Intel | Вертикальная интеграция | Возвращение технического лидерства | Новая упаковка, чипы ИИ, квантовые вычисления |

Samsung | Литейное производство и чип памяти | Расширенные узлы | Новые идеи в области микросхем памяти и логики |

Вы выбираете литейное производство, которое соответствует вашим потребностям. Некоторые литейные производства производят микросхемы меньшего размера и с большей скоростью. Другие работают над новыми корпусами или специальными функциями. Этап подготовки к печати зависит от того, что литейное производство делает лучше всего.

Изготовление — очень важная часть цикла проектирования СБИС. Необходимо соблюдать каждый этап, чтобы получить качественные микросхемы после монтажа.

Тестирование и упаковка

Электрические испытания

Необходимо проверить каждую микросхему перед тем, как она покинет завод. Электрические испытания позволяют убедиться в правильной работе микросхемы. Этот этап помогает выявить проблемы, возникшие при её изготовлении. Существуют различные способы проверки микросхем. Вот некоторые из наиболее распространённых:

Моделирование разломов

Автоматическая генерация тестовых шаблонов (ATPG)

Тестирование периферийного сканирования (JTAG)

Функциональное тестирование

Параметрическое тестирование

DFT позволяет добавлять специальные функции при проектировании микросхемы. Эти функции упрощают тестирование. Встроенная самодиагностика (BIST) позволяет микросхеме тестировать себя самостоятельно. Для этого не требуются дополнительные инструменты. ATPG создаёт тестовые шаблоны для быстрого поиска неисправностей. Эти методы помогают сэкономить деньги и время. Вы можете устранить проблемы до того, как микросхема попадёт к клиентам. Качественное тестирование означает, что пользователи получат только исправные микросхемы. Это способствует удовлетворенности пользователей.

Совет: Электрическое тестирование помогает обнаружить дефекты на ранней стадии. Оно гарантирует корректную работу микросхемы СБИС.

Методы упаковки

После тестирования необходимо защитить чип и подключить его. Упаковка делает это за вас. Способ упаковки чипа влияет на его работу. Он также влияет на срок его службы. Необходимо учитывать тепло, электропитание и сигналы.

Технология межсоединений играет важную роль в упаковке. Микро-бугоркиСквозные кремниевые переходные отверстия (TSV) и слои перераспределения (RDL) обеспечивают соединение кристалла. Микровыступы хороши для соединения кристалла с подложкой. Но они могут создавать проблемы из-за нагрева и вибрации. Электромиграция и тепловая миграция могут снизить надежность.

TSV позволяют сигналам и теплу перемещаться вверх и вниз по чипу. Это улучшает его работу. Однако различные материалы могут треснуть или сломаться при нагревании или охлаждении чипа.

Чтобы улучшить упаковку, необходимо изучить тепло, электричество и силу. Использование новых материалов, таких как высокоплотные межсоединения и современные термоматериалы, помогает контролировать тепло. Это также продлевает срок службы чипа. По мере того, как чипы становятся быстрее и компактнее, хороший дизайн упаковки становится всё важнее.

Ты это видишь тестирование и упаковка Оба важны. Они обеспечивают бесперебойную работу и долгий срок службы вашего чипа.

Кремниевая проверка

После завершения создания чипа необходимо проверить его работоспособность. Этот этап называется валидацией кремния. Необходимо убедиться, что чип соответствует исходному проекту и хорошо работает в реальных условиях.

Проверки после изготовления

После изготовления вы тестируете первые чипы, поступающие с завода. Эти чипы называются прототипами. Вы устанавливаете их на специальные платы и проводите множество тестов. Вы ищете проблемы, которые не были выявлены во время предыдущих проверок. Иногда ошибки не обнаруживаются на первом этапе тестирования. Теперь вы можете их обнаружить, потому что чип работает на реальной системной частоте.

Вы следуете стандартному процессу проверки кремния:

Предварительная проверка кремния Использует программное обеспечение для тестирования вашего чипа перед его изготовлением. Тестовые случаи запускаются в симуляторе. На этом этапе проверяется соответствие вашего RTL-кода спецификации.

Пост-кремниевая валидация начинается после получения реального чипа. Вы тестируете чип на оборудовании. Вы видите, как он работает в реальном времени и в реальных условиях.

Примечание: проверка после изготовления кремния помогает обнаружить проблемы, которые проявляются только тогда, когда чип работает на полной скорости или в реальной среде.

Конечный продукт

После завершения всех проверок вы узнаете, готов ли ваш чип к выпуску на рынок. Вы проверяете его производительность, энергопотребление и соответствие всем вашим целям. Если вы обнаружите проблемы, вы сможете их устранить, прежде чем производить новые чипы.

Вот простая таблица, показывающая разницу между этапами до и после получения кремния:

Шаг | Когда это произойдет | Что вы тестируете | Скорость тестирования |

|---|---|---|---|

Предварительная проверка кремния | Перед изготовлением | Программный симулятор | Нереальная скорость системы |

Пост-кремниевая валидация | После изготовления | Реальное оборудование | Реальная скорость системы |

Вам необходима валидация кремниевой микросхемы, чтобы убедиться, что ваша сверхбольшая интегральная схема (СБИС) работает так, как вы планировали. Этот этап даёт вам уверенность в том, что ваша разработка будет успешно реализована в реальных условиях.

Выполняя все этапы проектирования СБИС, вы повышаете надёжность. Это позволяет избежать ошибок и обеспечить стабильность работы. Знание процесса проектирования СБИС помогает улучшить скорость, размер и энергопотребление. Новые возможности, такие как Автоматизация на основе ИИ и 3D-интеграция меняют будущее VLSI. Если вы хотите профессионального роста, осваивайте новые навыки, получайте сертификатыи пообщайтесь с экспертами. Этот цикл поможет вам создавать более качественные чипы и оставаться лидерами в сфере технологий.

тенденция | Влияние на полупроводниковую технологию |

|---|---|

Автоматизация проектирования на основе ИИ | Ускоряет и упрощает проектирование микросхем |

Стратегии оптимизации энергопотребления | Помогает небольшим устройствам работать лучше |

Методы 3D-интеграции | Обеспечивает лучшую скорость и контроль температуры |

Подходы, ориентированные на безопасность | Защищает чипы от хакеров |

Расширенные инструменты моделирования | Проверяет проекты быстрее и точнее |

Проверьте, что вы знаете, и исправьте слабые места.

Посещайте специальные занятия.

Встречайтесь и общайтесь с людьми, работающими на местах.

FAQ

Что такое цикл проектирования СБИС?

Вы следуете циклу проектирования СБИС, чтобы создать микросхему шаг за шагом. Этот цикл поможет вам спланировать, собрать и протестировать микросхему. Каждый этап гарантирует её работоспособность и соответствие вашим требованиям.

Почему СБИС важны в электронике?

С помощью СБИС можно разместить миллионы мельчайших деталей на одном кристалле. Это делает устройства компактнее, быстрее и умнее. Телефоны, компьютеры и автомобили — все они используют СБИС для повышения эффективности работы.

С чего начать дизайн-проект?

Начните с описания того, что должен делать ваш чип. Вы ставите чёткие цели и перечисляете функции. Это помогает вам и вашей команде сохранять концентрацию и избегать ошибок.

Какие инструменты помогают в проектировании СБИС?

Ты используешь специальное программное обеспечение для рисования, протестируйте и проверьте свой чип. Такие инструменты, как Synopsys, Mentor Graphics и Cadence, помогут вам спроектировать, смоделировать и проверить чип перед его изготовлением.

Можно ли исправить ошибки после создания чипа?

В ходе тестирования можно обнаружить и исправить некоторые ошибки. Если же вы обнаружите серьёзные проблемы, вам, возможно, придётся изменить конструкцию и создать новый чип. Тщательное планирование поможет вам избежать дорогостоящих ошибок.