Možno sa pýtate, čo je to návrhový cyklus VLSI. Tento proces vám pomôže krok za krokom vytvoriť funkčný čip. Pri veľmi rozsiahlej integrácii sa používa polovodičová technológia. To vám umožňuje umiestniť milióny tranzistorov na jeden čip. Každá fáza cyklu je dôležitá. Ak krok vynecháte, môžu sa vyskytnúť chyby alebo čip, ktorý nebude fungovať. Oblasť VLSI sa rozrástla veľmi rýchlo. Globálny trh mal hodnotu približne 634.85 miliardy USD v roku 2025Do roku 2034 môže dosiahnuť 1 055,39 miliardy USD. V cykle zvyčajne sledujete tieto hlavné fázy:

Zhromažďovanie požiadaviek

Návrh na úrovni systému

Návrh RTL

Funkčné overenie

syntéza

Miesto a trasa

Fyzické overenie

Polovodičová technológia ovplyvňuje elektroniku, ktorú používate každý deň.

špecifikácia

Fáza špecifikácie je prvým krokom v cykle návrhu VLSI. V nej sa rozhodujete, čo by mal čip robiť. Taktiež sa rozhodujete, ako dobre by mal fungovať. Tento krok vám pomôže robiť správne rozhodnutia neskôr. Ak tento krok urobíte dobre, váš čip bude pravdepodobne fungovať. Môžete sa tiež vyhnúť veľkým chybám a ušetriť čas.

Požiadavky

Musíte mať jasné požiadavky Predtým, ako začnete s návrhom VLSI čipu. Tieto požiadavky hovoria, čo by mal čip robiť. Tiež hovoria, aký rýchly, aký výkonný a aký veľký by mal byť čip. Uvediete všetky funkcie, ktoré čip potrebuje. Zapísanie týchto podrobností pomáha každému poznať ciele. Zabezpečuje to, aby návrh spĺňal to, čo ľudia chcú.

Tip: Požiadavky píšte jednoduchými slovami. Používajte krátke vety. Snažte sa nepoužívať zložité slová.

Mnoho tímov používa rôzne spôsoby organizácie svojich požiadaviek. Tu je tabuľka s niektorými bežnými metódami:

metodológie | Popis |

|---|---|

SystemVerilog | Má veľa nástrojov na kontrolu funkčnosti čipu. Používa objektovo orientované programovanie a náhodné testovanie. |

Univerzálna overovacia metodika (UVM) | Používa SystemVerilog. Pomáha tímom vytvárať testy, ktoré sa dajú znova použiť. |

VHDL | Často sa používa na písanie a kontrolu návrhov čipov. Pomáha pri modelovaní a testovaní hardvéru. |

e (Špecifikácia) | Má silné nástroje na kontrolu čipov. Používa náhodné testovanie s pravidlami. |

C/C++ a Python | Používa sa na výrobu testovacích systémov a testovacích stolíc. |

Ciele systému

Nastavíš systémové ciele aby pomohli s usmernením návrhu. Medzi tieto ciele patrí rýchlosť čipu. Zahŕňajú aj jeho cenu a spotrebu energie. Vy rozhodujete o tom, ako bude čip fungovať s inými zariadeniami. Taktiež plánujete zmeny v budúcnosti. Stanovenie cieľov pomáha tímu udržať sa na správnej ceste.

Fáza špecifikácie je pri návrhu čipov VLSI veľmi dôležitá. Stanovuje základ pre celý proces. Dobrá špecifikácia zabezpečuje, že čip robí to, čo má. To je kľúčové pre úspech projektu.

architektúra

návrh systému

Začnete fáza architektúry plánovaním fungovania vášho čipu. Vy rozhodujete, čo bude každá časť čipu robiť. Taktiež si vyberáte, ako budú tieto časti medzi sebou komunikovať. Tento krok vám pomáha rozdeliť veľký problém na menšie a jednoduchšie úlohy. Pozriete sa na to, čo musí čip robiť, a vyberiete si najlepší spôsob, ako usporiadať jeho časti.

Môžete si vybrať z niekoľkých architektonických štýlovKaždý štýl má svoje silné stránky. Niektoré štýly vám umožňujú vyrobiť čip od základu. Iné používajú hotové súčiastky, aby ušetrili čas. Tu je tabuľka, ktorá zobrazuje niektoré bežné štýly a čo ich robí výnimočnými:

Architektonický štýl | Popis |

|---|---|

Plne zákazkový dizajn | Celý čip si zostavíte od základov. To vám poskytne najlepšiu rýchlosť a využitie energie, ale vyžaduje si to veľa času a zručnosti. |

Polo-zákazkový dizajn | Používate niektoré hotové diely a niektoré diely vyrobené na mieru. To šetrí čas a stále prináša dobré výsledky. |

Programovateľné logické obvody (PLD) | Fungovanie čipu môžete zmeniť po jeho výrobe. To je skvelé na rýchle testovanie nápadov. |

Návrh systému na čipe (SoC) | Na jeden čip umiestnite veľa súčiastok. Vďaka tomu je čip malý a rýchly. Vidíte to v telefónoch a inteligentných zariadeniach. |

Štandardný dizajn | Používate diely, ktoré sú už otestované a pripravené na použitie. Je to rýchle a funguje to dobre pre mnoho produktov. |

Tip: Vyberte si architektúru, ktorá zodpovedá potrebám vášho projektu. Premýšľajte o rýchlosti, výkone a o tom, koľko času máte k dispozícii.

Výber architektúry ovplyvňuje spotrebu energie vášho čipu a jeho rýchlosť. Na úsporu energie a zvýšenie rýchlosti môžete použiť špeciálne triky. Tu je niekoľko spôsobov, ako to dosiahnuť:

Technika | Popis |

|---|---|

Používajte komponenty s nízkou spotrebou energie | Vyberte si súčiastky, ktoré spotrebúvajú menej energie. Toto pomôže, ak váš čip funguje na batérie. |

Výkonové hradlovanie | Vypnite časti čipu, keď ich nepotrebujete. |

Dynamické škálovanie napätia a frekvencie (DVFS) | Zmeňte rýchlosť a spotrebu energie čipu na základe toho, čo robí. |

Cyklistika na plný úväzok | Obvody zapínajte iba vtedy, keď ich potrebujete. |

Minimalizujte prepínanie signálu | Znížte frekvenciu zmien signálov, aby ste ušetrili energiu. |

Optimalizácia kapacity záťaže | Znížte zaťaženie výstupov, aby ste spotrebovali menej energie. |

Viacprahový CMOS (MTCMOS) | Na úsporu energie v kľúčových oblastiach používajte rôzne typy vypínačov. |

Syntéza s ohľadom na energiu | Pri zostavovaní čipu si nastavte nástroje tak, aby sa zamerali na úsporu energie. |

Časové synchronizovanie v RTL | Zastavte hodiny v nepoužívaných častiach, aby ste znížili plytvanie energiou. |

Predpojatosť tela | Zmeňte napätie, aby ste znížili úniky a ušetrili energiu. |

Hierarchické mocenské domény | Rozdeľte čip do zón pre lepšiu kontrolu výkonu. |

Použitie technológie FinFET | Používajte špeciálne tranzistory, ktoré menej unikajú a dobre fungujú pri nízkom výkone. |

Bloková schéma

Nakreslíte blokovú schému, ktorá ukazuje, ako váš čip funguje. Táto schéma používa jednoduché tvary na znázornenie každej časti čipu. Tieto tvary spojíte čiarami, aby ste ukázali, ako sa dáta pohybujú. Dobrá bloková schéma pomáha každému pochopiť plán čipu.

Pri vytváraní blokovej schémy by ste mali:

Zobraziť všetky hlavné časti čipu.

Nakreslite jasné hranice pre tok údajov.

Označte každý blok jeho úlohou.

Udržujte diagram jednoduchý a ľahko čitateľný.

Jasná bloková schéma vám pomôže včas odhaliť problémy. Taktiež pomôže vášmu tímu prediskutovať čip a vykonať zmeny ešte predtým, ako začnete s jeho vývojom.

Dizajn zľava doprava

Fáza návrhu RTL je miesto, kde premieňate svoje nápady na kód, ktorý popisuje, ako váš čip funguje. Na písanie tohto kódu používate jazyk ako Verilog alebo VHDL. Zameriavate sa na to, ako sa dáta pohybujú a ako sa správa každá časť čipu. Táto fáza je dôležitá, pretože stanovuje pravidlá pre fungovanie vášho čipu.

Kódovanie RTL

Návrh RTL kódu začínate písaním kódu, ktorý ukazuje, čo každý blok robí. Zatiaľ sa nestaráte o fyzické rozloženie. Popíšete logiku a to, ako signály idú. Používate jednoduché príkazy na znázornenie toho, ako by mal čip reagovať na vstupy. Uistíte sa, že každá časť funguje podľa plánu.

Tip: Píšte jasný a jednoduchý kód. Na vysvetlenie zložitých častí použite komentáre. To vám a vášmu tímu pomôže neskôr pochopiť dizajn.

Počas návrhu RTL čelíte niekoľkým výzvam. Tu je tabuľka, ktorá zobrazuje tie najbežnejšie:

Vyzvať | Popis |

|---|---|

Zložitosť dizajnu | Musíte zvládať rozsiahle návrhy. Viac dielov znamená viac šancí na chyby a dlhší pracovný čas. |

Zabezpečenie správnosti návrhu | Musíte skontrolovať, či váš kód zodpovedá tomu, čo má čip robiť. |

Riadenie spotreby energie | Hľadáte spôsoby, ako ušetriť energiu a zároveň zachovať dobrý chod čipu. |

Musíte venovať pozornosť týmto problémom. Ak tak neurobíte, môžete skončiť s chybami alebo čipom, ktorý spotrebuje príliš veľa energie.

Funkčné overenie

Po dokončení kódovania RTL prejdete k overeniu návrhu. Otestujete svoj kód, aby ste sa uistili, že funguje podľa očakávaní. Používate testovacie lavice a simulačné nástroje. Pred zostavením čipu skontrolujete každú časť návrhu RTL, aby ste našli chyby.

Vykonáte veľa testov, aby ste zistili, či čip reaguje správne. Hľadáte chyby a včas ich opravíte. Overenie návrhu vám pomôže vyhnúť sa nákladným chybám neskôr. Tento proces opakujete, kým si nebudete istí, že váš návrh RTL zodpovedá vašim cieľom.

Poznámka: Dobré overenie návrhu šetrí čas a peniaze. Odhalíte problémy skôr, ako sa z nich stanú väčšie problémy.

Musíte si uvedomiť, že návrh RTL je kľúčovým krokom pri výrobe spoľahlivého čipu. Starostlivé kódovanie a dôkladné overenie návrhu vám pomôžu vytvoriť čip, ktorý funguje dobre a spĺňa vaše potreby.

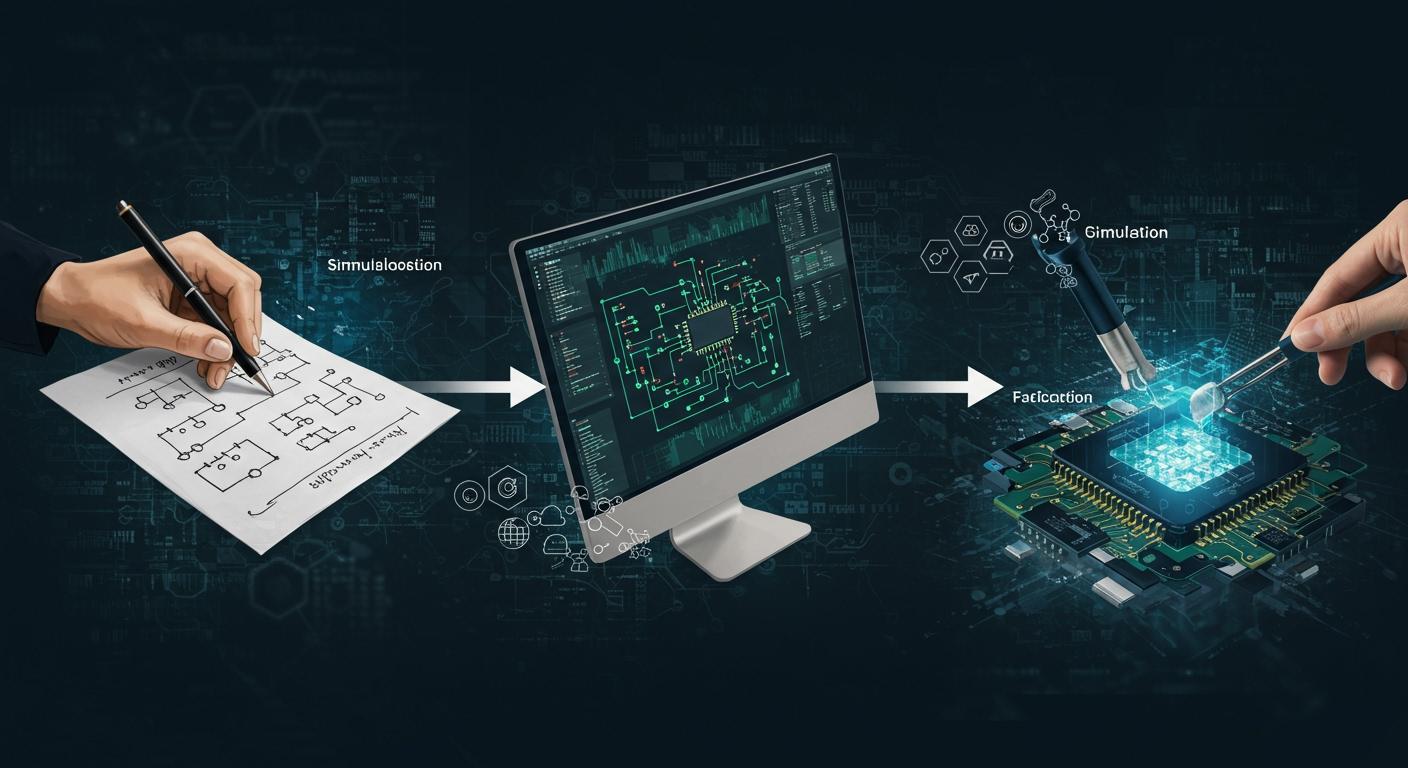

Prehľad postupu návrhu VLSI

Keď sa začnete učiť o návrhovom cykle VLSI, uvidíte, že postup návrhu VLSI vám poskytuje jasnú cestu od nápadu k funkčnému čipu. Tento postup vám pomáha vyhnúť sa chybám a zabezpečuje, aby návrh vášho čipu fungoval podľa plánu.

Fázy v procese návrhu VLSI

V postupe návrhu VLSI budete postupovať podľa súboru krokov. Každý krok nadväzuje na predchádzajúci. Tu je obvyklé poradie, ktoré uvidíte v postupe:

Konceptualizácia a špecifikácia

Architektonický dizajn

Logický dizajn

Syntéza RTL

Netlist a plánovanie poschodí

Umiestnenie a smerovanie

Fyzické overenie

Analýza časovania

Extrakcia a simulácia

Odlepenie pásky

Kľúčové aktivity

Všimnete si, že každá fáza v tomto postupe má špecifickú úlohu. Postup návrhu VLSI začína jasným plánom a končí skutočným čipom. Svoju prácu kontrolujete v každom kroku. To vám pomôže včas odhaliť problémy. Môžete ich opraviť skôr, ako sa rozrastú. Postup zahŕňa kroky ako špecifikácia, zadanie návrhu, syntéza, overenie, rozloženie a výroba. Každý z nich vám pomôže uistiť sa, že návrh vášho čipu je správny. Tento starostlivý cyklus udržiava nízke chyby a vysokú kvalitu.

Uvidíte, že postup je vaším sprievodcom pre každý VLSI projekt. Dodržiavaním postupu urobíte svoj čip silným a spoľahlivým. Postup je chrbticou každého úspešného VLSI čipu.

Logická syntéza

RTL k bránam

Logická syntéza je kľúčovým krokom k premene vašich nápadov na skutočný hardvér. V tejto fáze vezmete svoj RTL kód a zmeníte ho na logické brány. Na túto prácu použijete špeciálne nástroje. Tieto nástroje čítajú váš RTL kód a vytvárajú sieť brán, ktoré je možné zostaviť na čipe.

Uvidíte tri hlavné kroky v logickej syntéze:

Preklad: Nástroj zmení váš kód RTL do formy, ktorá používa booleovské rovnice. Tento krok nezávisí od technológie čipu.

Optimalizácia: Nástroj zjednodušuje booleovské rovnice. Na to používa metódy ako súčet súčinov.

Mapovanie technológií: Nástroj porovnáva optimalizované rovnice so skutočnými hradlami z knižnice. Vyberá hradly, ktoré zodpovedajú vašim konštrukčným potrebám.

Tip: Pred začatím syntézy vždy skontrolujte kód RTL, či neobsahuje chyby. Čistý kód vám pomôže dosiahnuť lepšie výsledky.

Optimalizácia

Optimalizácia vám pomôže nájsť najlepší čip pre vaše potreby. Chcete, aby váš čip bol malý, rýchly a spotrebovával málo energie. Nástroje logickej syntézy vám pomôžu dosiahnuť tieto ciele tým, že počas procesu robia inteligentné rozhodnutia.

Tu je tabuľka, ktorá ukazuje, ako optimalizácia ovplyvňuje váš čip:

Aspekt | Vplyv na VLSI čipy |

|---|---|

Optimalizácia oblasti | Znižuje fyzickú stopu, čo umožňuje umiestniť viac čipov na jeden wafer, čo vedie k vyššiemu výťažku a nižším nákladom. |

Optimalizácia rýchlosti | Rýchlejšie siete často vedú k väčšej spotrebe plochy, čo si vyžaduje kompromisy medzi rýchlosťou a plochou. |

Spotreba energie | Väčšie hradlá zvyšujú kapacitu, čo vedie k vyššej spotrebe energie počas prepínania. |

Musíte vyvážiť plochu, rýchlosť a spotrebu energie. Ak zrýchlite čip, môže sa zväčšiť a spotrebovať viac energie. Ak ho zmenšíte, môže bežať pomalšie. Dobrá logická syntéza vám pomôže nájsť najlepšiu rovnováhu.

Optimalizácia plochy umožňuje umiestniť viac čipov na jeden wafer. To znižuje náklady a umožňuje pridať viac funkcií.

Optimalizácia rýchlosti umožňuje čipu pracovať rýchlejšie, ale môže spotrebovať viac miesta a energie.

Efektívne využitie priestoru je dôležité pre pridávanie nových funkcií bez zníženia výkonu.

Logickú syntézu používate v každom VLSI projekte. Tvaruje váš návrh a pomáha vám vytvárať čipy, ktoré dobre fungujú v reálnom svete.

Fyzický dizajn

fáza fyzického návrhu je to krok, kde premeníte logiku vášho čipu na skutočné rozloženie. Vy rozhodujete, kam pôjde každá časť čipu a ako ich budú vodiče prepájať. Tento krok je dôležitý pri fyzickom návrhu VLSI, pretože ovplyvňuje, ako dobre váš čip bude fungovať a či sa dá vyrobiť bez problémov.

Plánovanie poschodí

Fázu fyzického návrhu začínate plánovaním podlahy. Tu rozdelíte čip na bloky a každému bloku pridelíte vlastný priestor. Premýšľate o tom, aký veľký by mal byť každý blok a kam ho umiestniť. Dobré plánovanie podlahy vám pomôže vyhnúť sa preplneným oblastiam a zabezpečí rýchly prenos signálov. Taktiež naplánujete priestor pre napájacie a hodinové vedenia. Tento krok nastavuje štruktúru pre zvyšok procesu fyzického návrhu VLSI.

V tejto fáze vám s plánovaním podlahy a ďalšími úlohami pomôže veľa nástrojov. Medzi najobľúbenejšie nástroje patria:

Kompilátor Synopsys IC II: Rýchle umiestňovanie a smerovanie, návrh s ohľadom na spotrebu energie.

Mentor Graphics Calibre: Kontroluje pravidlá a porovnáva rozloženie so schémou.

ANSYS RedHawk: Kontroluje napájanie a spoľahlivosť.

Tanner Tools: Vhodné pre analógové a zmiešané rozloženie signálu.

Avanti Hercules: Kontroluje integritu signálu a napájania.

OpenROAD: Nástroj s otvoreným zdrojovým kódom pre fyzický dizajn.

KLATencor L-Edit: Používa sa na vlastné rozloženie integrovaných obvodov.

Tip: Vyberte si nástroj, ktorý vyhovuje potrebám vášho projektu a zručnostiam vášho tímu.

Umiestnenie a smerovanie

Po plánovaní priestoru prejdete k umiestneniu a smerovaniu. Každú bunku alebo blok umiestnite na jej miesto. Chcete udržať súvisiace bloky blízko seba. To pomáha signálom prenášať sa rýchlejšie a šetrí energiu. Tiež zabezpečíte, aby sa čip príliš neprehrial.

Ďalej smerujete vodiče. Nakreslíte cesty pre signály medzi blokmi. Vyvážite rýchlosť a vyhnete sa preplneným cestám. Taktiež skontrolujete, či vaše rozloženie dodržiava pravidlá pre výrobu čipov. Tieto kroky pomôžu vášmu čipu dobre fungovať a uľahčia jeho výrobu.

Vo fáze fyzického návrhu postupujete podľa týchto hlavných krokov:

Rozdeľte a rozvrhnite čip.

Umiestnite bunky a bloky.

Postavte strom hodín.

Veďte káble.

Skontrolujte pravidlá a vyrobiteľnosť.

Optimalizujte výkon.

Keď dokončíte fázu fyzického návrhu, máte rozloženie pripravené na výrobu. Tento krok je kľúč pre každý VLSI projekt.

Dizajn pre testovateľnosť

Keď pracujete na VLSI čipe, chcete sa uistiť, že ho môžete ľahko otestovať. Návrh pre testovateľnosť vám pomôže včas odhaliť problémy a opravíte ich skôr, ako sa čip dostane k zákazníkom. Do čipu pridáte špeciálne funkcie, aby ste mohli skontrolovať, či všetko funguje podľa plánu. Tieto funkcie urýchľujú testovanie a pomáhajú vám ušetriť peniaze počas výroby.

Testovacie funkcie

Na zlepšenie testovateľnosti vášho čipu používate niekoľko techník. Tieto metódy vám pomôžu odhaliť chyby a zabezpečiť, aby váš čip fungoval správne.

Návrh skenovania vám umožňuje ovládať a kontrolovať klopné obvody vo vnútri čipu počas testov.

Hraničné skenovanie vám pomáha testovať pripojenia medzi čipmi na doske bez použitia sond.

Vstavaný autotest (BIST) pridáva testovací hardvér do čipu, aby sa mohol sám otestovať.

Memory BIST (MBIST) kontroluje pamäťové bloky vo vnútri vášho čipu.

ATPG (Automatické generovanie testovacích vzorov) vytvára vzory, ktoré vám pomôžu nájsť chyby po výrobe.

Tieto funkcie zvyšujú pokrytie testovaním a skracujú čas potrebný na testovanie. Môžete rýchlo nájsť chyby a vyhnúť sa odosielaniu chybných čipov zákazníkom.

Tip: Pridajte testovacie funkcie včas vo vašom procese návrhu. To uľahčuje testovanie a znižuje náklady.

Pri použití týchto techník uvidíte mnoho výhod. Tabuľka nižšie ukazuje, ako návrh pre testovateľnosť pomáha vášmu čipu:

Prospech | Popis |

|---|---|

Detekcia poruchy | |

Zlepšenie výnosu výroby | Opravíte problémy počas výroby a získate viac dobrých štiepok. |

Spoľahlivosť | Zabezpečíte, aby váš čip fungoval dobre dlhú dobu. |

Zložité čipy môžete testovať rýchlejšie a presnejšie. Dodávate vysokokvalitné čipy, ktoré fungujú podľa očakávaní.

Skenovacie reťazce

Skenovacie reťazce hrajú veľkú úlohu pri testovaní VLSI čipov. Klopné obvody sa zapájajú do reťazca, aby ste mohli počas testov nastavovať a čítať ich hodnoty. Toto nastavenie vám umožňuje skontrolovať vnútro čipu bez toho, aby ste ho museli rozoberať.

Na nájdenie chýb v logických blokoch používate skenovacie reťazce. Ovládate každý klopný obvod a sledujete, ako sa signály pohybujú cez váš čip. Táto metóda vám pomáha odhaliť problémy, ktoré by bežné testy mohli prehliadnuť.

Pridaním skenovacích reťazcov uľahčíte testovanie čipu a zvýšite jeho spoľahlivosť. Znížite tiež riziko nákladných porúch po tom, čo sa váš čip dostane do produktov.

Poznámka: Ak si dobre naplánujete skenovacie reťazce, môžete ušetriť čas a zlepšiť kvalitu čipu.

Včasná integrácia dizajnu pre testovateľnosť vám pomôže skrátiť čas testovania a vyhnete sa drahým chybám. Vytvárate čipy, ktoré vydržia dlhšie a fungujú lepšie.

Analýza časovania

Analýza časovania vám pomáha zabezpečiť, aby váš čip pracoval správnou rýchlosťou. Tento krok použijete na kontrolu, či signály prechádzajú čipom dostatočne rýchlo. Ak analýzu časovania vynecháte, váš čip nemusí fungovať podľa plánu. Vo VLSI je analýza časovania jednou z najdôležitejších kontrol pred dokončením návrhu.

Statické časovanie

Používaš statická analýza časovania (STA) na kontrolu načasovania vášho čipu bez spustenia testovacích vzorov. STA skúma každú cestu vo vašom obvode a kontroluje, či signály prichádzajú včas. Táto metóda vám pomáha včas nájsť problémy. Nemusíte používať vstupné vektory, takže môžete rýchlo skontrolovať všetky možné cesty.

Tu sú niektoré bežné metódy analýzy načasovania mohli by ste použiť:

Statická analýza časovania (STA)

Dynamická analýza časovania (DTA)

Štatistická statická analýza času (SSTA)

Analýza načasovania odhlásenia

Analýza viacerých rohov a viacerých módov (MCMM)

Analýza variácií na čipe (OCV)

STA zohráva dôležitú úlohu v predchádzaní narušeniam časovania. Chcete, aby signály dorazili k klopným obvodom a registrom v správnom okamihu. Ak signály prídu príliš neskoro alebo príliš skoro, váš čip by mohol zlyhať. Viac ako 80 % konštrukčných zlyhaní v kremíku sa vyskytujú kvôli porušeniam časovania. STA vám pomáha vyhnúť sa týmto nákladným chybám.

Poznámka: Statická analýza časovania kontroluje maximálnu rýchlosť vášho čipu a zabezpečuje, aby všetky signály dorazili včas. Tento krok je nevyhnutný pre funkčný čip.

Časová uzávierka

Časové uzavretie je proces, pri ktorom opravíte všetky problémy s časovaním vo vašom čipe. Chcete, aby každý signál splnil svoj časový cieľ. Možno budete musieť zmeniť dizajn, presunúť bloky alebo upraviť dĺžky vodičov. Časové uzavretie môže vyžadovať veľa úsilia, ale je kľúčové pre funkčný čip.

Na dosiahnutie časového uzavretia postupujte podľa týchto krokov:

Analyzujte hlásenia o načasovaní od STA.

Nájdite cesty, ktoré zlyhávajú v načasovaní.

Zmeňte svoj dizajn, aby ste opravili tieto cesty.

Znova spustite nástroj STA a skontrolujte, či ste problémy vyriešili.

Opakujte, kým nedosiahnete časový limit.

Na pomoc s časovým uzatváraním môžete použiť špeciálne nástroje. Tieto nástroje vám ukážu, ktoré cesty potrebujú úpravu. Môžete zmeniť svoj návrh a rýchlo vidieť výsledky. Časové uzatváranie zabezpečí, že váš čip bude fungovať požadovanou rýchlosťou.

Tip: Začnite pracovať na načasovaní uzávierky v dostatočnom predstihu. Oprava problémy s načasovaním na konci to môže byť veľmi ťažké.

Pred dokončením návrhu VLSI potrebujete časové uzatvorenie. Tento krok vám dáva istotu, že váš čip bude fungovať v reálnom živote.

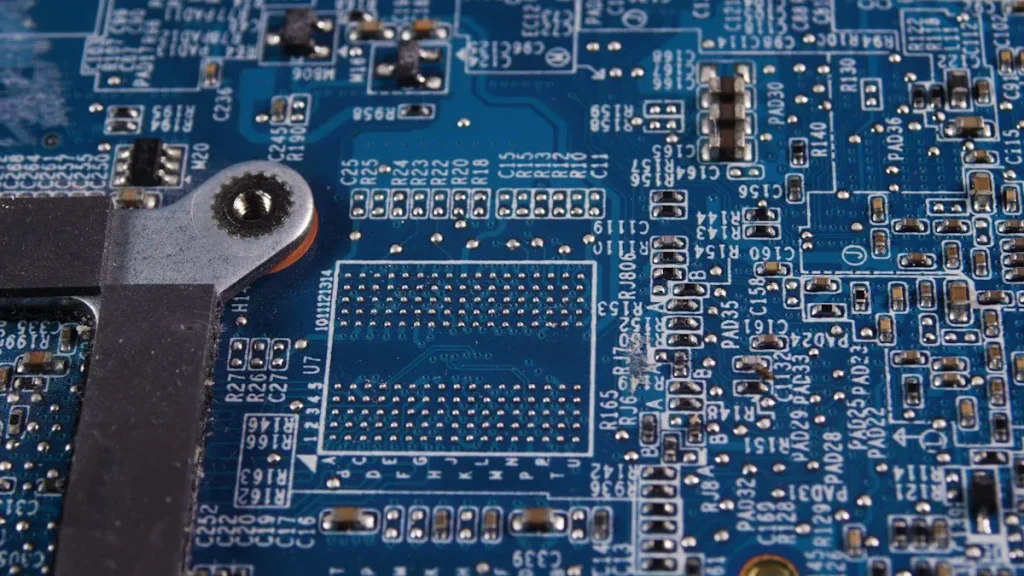

Fyzické overenie

Fyzické overovacie kontroly Ak je rozloženie vášho čipu pripravené na výrobu, chcete si byť istí, že váš čip bude fungovať a bude spĺňať všetky pravidlá zlievarne. Tento krok vám pomôže nájsť chyby pred výrobou čipu. Použijete rôzne kontroly, aby ste zistili, či je vaše rozloženie bezpečné a správne.

Tu je tabuľka, ktorá uvádza hlavné kroky fyzického overenia a čo robia:

Krok overenia | Účel |

|---|---|

Kontrola pravidiel návrhu (DRC) | Skontroluje, či rozloženie zodpovedá pravidlá zlievarne pre šírku a medzery. |

Rozloženie vs. schéma (LVS) | Uisťuje sa, že rozloženie zodpovedá plánu zapojenia alebo schéme. |

Kontrola elektrických predpisov (ERC) | Nájde elektrické problémy, ako sú chýbajúce vodiče alebo príliš vysoká kapacita. |

DRC

Začnete kontrolou pravidiel návrhu, nazývanou DRC. Táto kontrola porovná rozloženie vášho čipu s pravidlami zlievarne. Tieto pravidlá určujú, aké široké musia byť vodiče a ako ďaleko od seba by mali zostať. Ak tieto pravidlá porušíte, váš čip nemusí fungovať alebo by sa mohol ťažko vyrábať.

DRC je súčasťou fyzického overovaniaPomáha vám nájsť problémy, ako sú príliš blízko seba umiestnené vodiče alebo príliš malé tvary. Oprava týchto problémov uľahčuje výrobu čipu a zvyšuje jeho spoľahlivosť.

Proces | Sústrediť | Účel |

|---|---|---|

DRC | Fyzické overenie | Zaisťuje, že čip je možné vyrobiť podľa pravidiel návrhu. |

Tip: Pred dokončením rozloženia vždy spustite DRC. Tento krok šetrí čas a peniaze.

LVS

Po DRC vykonáte kontrolu Layout vs Schematic alebo LVS. Táto kontrola zabezpečí, aby sa vaše rozloženie zhodovalo s vaším plánom zapojenia. Chcete, aby každý vodič a súčiastka vo vašom rozložení zodpovedala vašej schéme zapojenia.

LVS sa zaoberá elektrickým overovaním. Skontroluje, či váš čip bude fungovať podľa plánu. Ak LVS zistí niečo zlé, musíte to opraviť predtým, ako budete pokračovať.

Proces | Sústrediť | Účel |

|---|---|---|

LVS | Elektrické overenie | Zabezpečuje, aby rozloženie zodpovedalo schéme pre správnu prácu. |

Fyzické overenie je dôležitou súčasťou procesu VLSI. Keď používate DRC a LVS, uistíte sa, že váš návrh je správny a pripravený na ďalší krok.

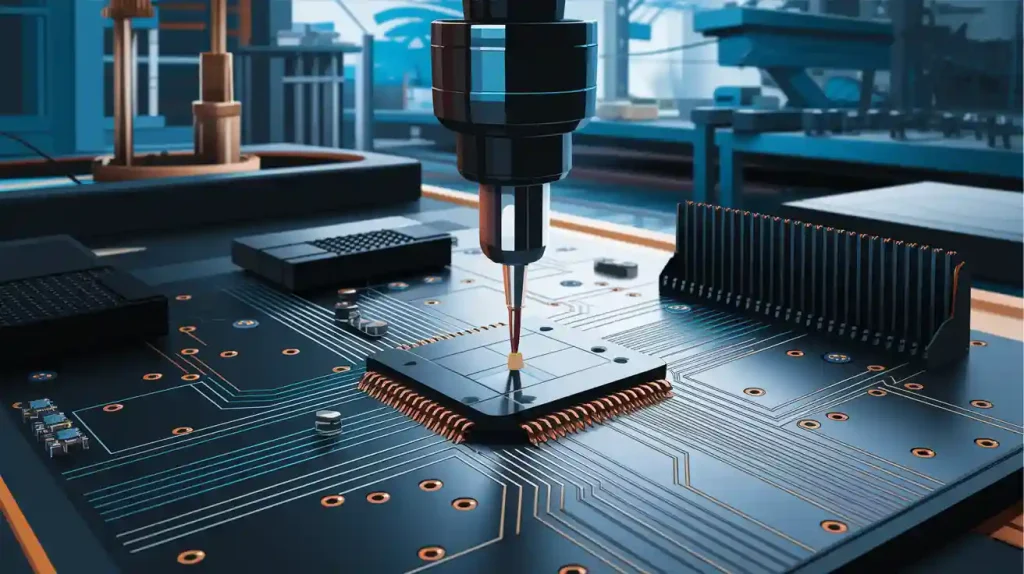

Výrobné

Po dokončení odstraňovania pásky v cykle návrhu VLSI začnete výmyselTento krok premení váš návrh čipu na skutočnú vec. Vaše nápady sa premenia na kremíkové čipy. Tieto čipy sa používajú v telefónoch, počítačoch a iných zariadeniach.

Spracovanie oblátok

Spracovanie oblátok je prvá časť výroby čipov. Použijete tenký kúsok kremíka nazývaný doštička. Postupujete podľa mnohých krokov na vytvorenie vrstiev a obvodov na ňom. Každý krok pridáva k vášmu čipu niečo dôležité.

Tu sú hlavné kroky spracovania doštičiek:

Povrchové čistenie

Oblátku vyčistíte, aby ste sa zbavili prachu.Počiatočná oxidácia

Na doštičke vypestujete tenkú vrstvu oxidu.CVD depozícia

Nové materiály sa nanášajú na doštičku pomocou špeciálneho plynu.Povlakový fotorezist

Oblátku pokryjete materiálom, ktorý reaguje na svetlo.Metalizácia a prepojenie

Na spojenie častí čipu pridáte kov.Chemické mechanické leštenie (CMP)

Oblátku vyleštíte, aby bola plochá a hladká.Záverečné testovanie a balenie

Otestujete čip a pripravíte ho na balenie.

Na výrobu zložitých čipov môžete niektoré kroky zopakovať. Každá fáza vám pomôže vytvoriť čip, ktorý zodpovedá vášmu plánu.

Tip: Starostlivé spracovanie doštičiek zabraňuje vzniku defektov a vytvára lepšie čipy.

Zlievareňské schody

Po spracovaní doštičky pošlete čip do zlievárne na výrobu pásky. Každá zlieváreň používa vlastné spôsoby výroby čipov. Majú odlišné obchodné štýly, technológie a výskumné ciele.

Tu je tabuľka, ktorá ukazuje, čo robia poprední výrobcovia:

Výrobca | Obchodný model | Zameranie uzla procesu | Zameranie na výskum a vývoj |

|---|---|---|---|

TSMC | Zlieváreň Pure-play | Menšie procesné uzly | Zlepšovanie procesných uzlov a zvyšovanie výnosov |

Intel | Vertikálna integrácia | Získanie späť technického lídra | Nové balenie, čipy s umelou inteligenciou, kvantové výpočty |

Samsung | Zlieváreň a pamäťový čip | Pokročilé uzly | Nové nápady v oblasti pamätí a logických čipov |

Vyberiete si zlievareň, ktorá vyhovuje vašim potrebám. Niektoré zlievarne vyrábajú menšie a rýchlejšie čipy. Iné pracujú na nových baleniach alebo špeciálnych funkciách. Váš krok odlepovania závisí od toho, v čom je zlievareň najlepšia.

Výroba je veľmi dôležitou súčasťou cyklu návrhu VLSI. Musíte dodržať každý krok, aby ste po odlepení pásky získali dobré čipy.

Testovanie a balenie

Elektrické skúšky

Predtým, ako opustí továreň, musíte skontrolovať každý čip. Elektrické testovanie zabezpečí, aby váš čip fungoval podľa plánu. Tento krok vám pomôže nájsť problémy s výrobou čipu. Na testovanie čipov sa používajú rôzne spôsoby. Niektoré bežné spôsoby sú:

Modelovanie porúch

Automatické generovanie testovacích vzorov (ATPG)

Testovanie hraničného skenovania (JTAG)

Funkčné testovanie

Parametrické testovanie

DFT vám umožňuje pridať špeciálne funkcie už pri návrhu čipu. Tieto funkcie zjednodušujú testovanie. Vstavaný autotest (BIST) umožňuje čipu testovať sa sám. Na to nepotrebujete žiadne ďalšie nástroje. ATPG vytvára testovacie vzory na rýchle nájdenie chýb. Tieto metódy vám pomáhajú ušetriť peniaze a čas. Môžete opraviť problémy skôr, ako zákazníci dostanú čip. Dobré testovanie znamená, že k používateľom sa dostanú iba funkčné čipy. To udržiava ľudí spokojných.

Tip: Elektrické testovanie vám pomôže včas odhaliť chyby. Zabezpečí to, aby váš VLSI čip fungoval správne.

Metódy balenia

Po testovaní musíte čip chrániť a pripojiť. Balenie túto úlohu urobí za vás. Spôsob, akým čip zabalíte, ovplyvňuje jeho funkčnosť. Ovplyvňuje aj jeho životnosť. Musíte zvážiť teplo, energiu a signály.

Technológia prepojenia je pri balení dôležitá. Mikrohrbolčeky, kremíkové priechodky (TSV) a redistribučné vrstvy (RDL) pomáhajú spojiť čip. Mikrovýstupky sú dobré pre prepojenie čipu so substrátom. Môžu však mať problémy s teplom a trasením. Elektromigracia a tepelná migrácia môžu znížiť spoľahlivosť.

TSV umožňujú signálom a teplu pohyb hore a dole v čipe. To pomáha čipu lepšie fungovať. Rôzne materiály však môžu prasknúť alebo sa zlomiť, keď sa čip zahreje alebo ochladí.

Pre zlepšenie balenia je potrebné študovať teplo, elektrinu a silu. Používanie nových materiálov, ako sú vysokohustotné prepojenia a pokročilé tepelné materiály, pomáha kontrolovať teplo. Taktiež predlžuje životnosť čipu. S rastúcou rýchlosťou a zmenšovaním čipov je dôležitý dobrý dizajn balenia.

To vidíš testovanie a balenie sú dôležité. Pomáhajú vášmu čipu dobre fungovať a vydržať dlho.

Validácia kremíka

Keď dokončíte výrobu čipu, musíte skontrolovať, či funguje podľa plánu. Tento krok sa nazýva validácia kremíka. Chcete sa uistiť, že váš čip zodpovedá pôvodnému návrhu a funguje dobre v reálnom živote.

Kontroly po výrobe

Po výrobe testujete prvé čipy, ktoré prichádzajú z továrne. Tieto čipy sa nazývajú prototypy. Umiestnite ich na špeciálne dosky a spustí sa množstvo testov. Hľadáte problémy, ktoré sa počas predchádzajúcich kontrol neprejavili. Niekedy sa chyby vyhnú prvému kolu testovania. Teraz ich môžete nájsť, pretože čip beží na skutočnej systémovej rýchlosti.

Pri overovaní kremíka postupujete podľa štandardného postupu:

Predsilikónové overenie používa softvér na testovanie čipu pred jeho výrobou. Spúšťate testovacie prípady v simulátore. Tento krok kontroluje, či váš kód RTL zodpovedá špecifikácii.

Post-kremíková validácia začína po získaní skutočného čipu. Čip otestujete na hardvéri. Uvidíte, ako funguje v reálnom čase a v reálnych podmienkach.

Poznámka: Post-silikónová validácia vám pomôže nájsť problémy, ktoré sa objavia iba vtedy, keď čip beží na plnej rýchlosti alebo v reálnom prostredí.

Finálny produkt

Keď dokončíte všetky kontroly, viete, či je váš čip pripravený na trh. Pozriete sa na to, ako čip funguje, koľko energie spotrebuje a či spĺňa všetky vaše ciele. Ak nájdete problémy, môžete ich opraviť pred výrobou ďalších čipov.

Tu je jednoduchá tabuľka, ktorá ukazuje rozdiel medzi krokmi pred kremíkom a po kremíku:

Krok | Keď sa to stane | Na čom testujete | Rýchlosť testovania |

|---|---|---|---|

Predsilikónové overenie | Pred zhotovením | Softvérový simulátor | Nie skutočná rýchlosť systému |

Post-silikónová validácia | Po výrobe | Skutočný hardvér | Skutočná rýchlosť systému |

Potrebujete validáciu kremíka, aby ste sa uistili, že váš VLSI čip funguje podľa plánu. Tento krok vám dáva istotu, že váš návrh bude v reálnom svete úspešný.

Spoľahlivejším návrhom VLSI čipov je dodržiavanie každej fázy. Týmto spôsobom sa môžete vyhnúť chybám a udržať si stabilnú prácu. Pochopenie postupu návrhu VLSI pomáha vám zlepšiť rýchlosť, veľkosť a využitie energie. Nové veci ako napríklad Automatizácia a 3D integrácia riadená umelou inteligenciou menia budúcnosť VLSI. Ak chcete vo svojej práci rásť, učte sa nové zručnosti, získajte certifikátya porozprávajte sa s odborníkmi. Cyklus vám pomôže vytvoriť lepšie čipy a udržať si náskok v oblasti technológií.

trend | Vplyv na polovodičovú technológiu |

|---|---|

Automatizácia dizajnu riadená umelou inteligenciou | Zrýchľuje a zjednodušuje návrh čipov |

Stratégie optimalizácie výkonu | Pomáha malým zariadeniam lepšie fungovať |

Techniky 3D integrácie | Poskytuje lepšiu rýchlosť a reguláciu tepla |

Prístupy zamerané na bezpečnosť | Chráni čipy pred hackermi |

Pokročilé simulačné nástroje | Kontroluje návrhy rýchlejšie a presnejšie |

Overte si, čo viete, a opravte slabé miesta.

Navštevujte špeciálne kurzy.

Stretávajte sa a rozprávajte sa s ľuďmi v teréne.

Často kladené otázky

Čo je to návrhový cyklus VLSI?

Postupne postupujete podľa cyklu návrhu VLSI a vytvárate čip. Tento cyklus vám pomôže naplánovať, zostaviť a otestovať váš čip. Každá fáza zabezpečí, aby váš čip fungoval správne a spĺňal vaše potreby.

Prečo je VLSI dôležitá v elektronike?

VLSI sa používa na umiestnenie miliónov drobných súčiastok na jeden čip. Vďaka tomu sú zariadenia menšie, rýchlejšie a inteligentnejšie. Telefóny, počítače a autá používajú VLSI čipy na lepšiu funkčnosť.

Ako začať s dizajnérskym projektom?

Začnete tým, že si zapíšete, čo chcete, aby váš čip robil. Stanovíte si jasné ciele a uvediete funkcie. To vám a vášmu tímu pomôže zostať sústredení a vyhnúť sa chybám.

Aké nástroje pomáhajú pri návrhu VLSI?

Používaš špeciálny softvér na kreslenie, otestujte a skontrolujte svoj čip. Nástroje ako Synopsys, Mentor Graphics a Cadence vám pomôžu navrhnúť, simulovať a overiť váš čip pred jeho výrobou.

Viete opraviť chyby po výrobe čipu?

Počas testovania môžete nájsť a opraviť niektoré chyby. Ak zistíte veľké problémy, možno budete musieť zmeniť dizajn a vyrobiť nový čip. Starostlivé plánovanie vám pomôže vyhnúť sa nákladným chybám.