Anda mungkin bertanya apa itu siklus desain VLSI. Proses ini membantu Anda membuat chip yang berfungsi langkah demi langkah. Dalam integrasi skala sangat besar, Anda menggunakan teknologi semikonduktor. Ini memungkinkan Anda menempatkan jutaan transistor dalam satu chip. Setiap tahap dalam siklus ini penting. Jika Anda melewatkan satu langkah, Anda mungkin mendapatkan kesalahan atau chip yang tidak berfungsi. Bidang VLSI telah berkembang sangat pesat. Pasar global bernilai sekitar USD 634.85 miliar pada 2025. Jumlahnya mungkin mencapai USD 1,055.39 miliar pada tahun 2034. Anda biasanya mengikuti tahapan-tahapan utama berikut dalam siklus tersebut:

pengumpulan kebutuhan

Desain tingkat sistem

desain RTL

Verifikasi fungsional

Sintesa

Tempat dan rute

Verifikasi fisik

Teknologi semikonduktor memengaruhi perangkat elektronik yang Anda gunakan sehari-hari.

Spesifikasi

Tahap spesifikasi adalah langkah pertama dalam siklus desain VLSI. Di sini, Anda menentukan apa yang seharusnya dilakukan oleh chip tersebut. Anda juga menentukan seberapa baik kinerjanya. Langkah ini membantu Anda membuat pilihan yang tepat nantinya. Jika Anda melakukan langkah ini dengan baik, chip Anda kemungkinan besar akan berfungsi dengan baik. Anda juga dapat menghindari kesalahan besar dan menghemat waktu.

Persyaratan

Anda harus memiliki persyaratan yang jelas Sebelum Anda memulai desain chip VLSI, persyaratan ini menjelaskan apa yang seharusnya dilakukan chip tersebut. Persyaratan ini juga menentukan seberapa cepat, seberapa besar daya, dan seberapa besar ukuran chip tersebut. Anda mencantumkan semua fitur yang dibutuhkan chip. Menuliskan detail ini membantu semua orang memahami tujuannya. Hal ini memastikan desain sesuai dengan keinginan orang-orang.

Tips: Tulis persyaratan dengan kata-kata yang mudah dipahami. Gunakan kalimat yang singkat. Usahakan untuk tidak menggunakan kata-kata yang sulit.

Banyak tim menggunakan berbagai cara untuk mengatur kebutuhan mereka. Berikut tabel dengan beberapa metode umum:

Metodologi | Uraian Teknis |

|---|---|

SistemVerilog | Memiliki banyak alat untuk memeriksa apakah chip berfungsi. Menggunakan pemrograman berorientasi objek dan pengujian acak. |

Metodologi Verifikasi Universal (UVM) | Menggunakan SystemVerilog. Sistem ini membantu tim membangun pengujian yang dapat digunakan kembali. |

VHDL | Banyak digunakan untuk menulis dan memeriksa desain chip. Membantu memodelkan dan menguji perangkat keras. |

e (Specman) | Memiliki alat yang kuat untuk memeriksa chip. Menggunakan pengujian acak dengan aturan. |

C/C++ dan Python | Digunakan untuk membuat sistem pengujian dan bangku pengujian. |

Tujuan Sistem

Anda yang mengatur tujuan sistem untuk membantu memandu desain. Sasaran ini mencakup seberapa cepat chip tersebut seharusnya, berapa biayanya, dan berapa banyak daya yang dapat digunakan. Anda memutuskan bagaimana chip tersebut akan bekerja dengan perangkat lain. Anda juga merencanakan perubahan di masa mendatang. Menetapkan sasaran membantu tim tetap berada di jalur yang tepat.

Tahap spesifikasi sangat penting dalam desain chip VLSI. Ini menjadi dasar bagi keseluruhan proses. Spesifikasi yang baik memastikan chip berfungsi sebagaimana mestinya. Ini adalah kunci keberhasilan proyek.

Arsitektur

Desain Sistem

Anda memulai fase arsitektur Dengan merencanakan cara kerja chip Anda, Anda memutuskan apa yang akan dilakukan setiap bagian chip. Anda juga memilih bagaimana bagian-bagian ini akan berkomunikasi satu sama lain. Langkah ini membantu Anda memecah masalah besar menjadi tugas-tugas yang lebih kecil dan lebih mudah. Anda melihat apa yang harus dilakukan chip dan memilih cara terbaik untuk mengatur bagian-bagiannya.

Anda dapat memilih dari beberapa gaya arsitekturSetiap gaya memiliki keunggulannya sendiri. Beberapa gaya memungkinkan Anda membuat chip dari awal. Gaya lainnya menggunakan komponen siap pakai untuk menghemat waktu. Berikut adalah tabel yang menunjukkan beberapa gaya umum dan apa yang membuat mereka istimewa:

Gaya arsitektur | Uraian Teknis |

|---|---|

Desain Kustom Penuh | Anda membangun seluruh chip dari awal. Ini memberi Anda kecepatan dan penggunaan daya terbaik, tetapi membutuhkan banyak waktu dan keterampilan. |

Desain Semi-Kustom | Anda menggunakan beberapa komponen siap pakai dan beberapa komponen khusus. Ini menghemat waktu dan tetap memberikan hasil yang baik. |

Perangkat Logika Terprogram (PLD) | Anda dapat mengubah cara kerja chip setelah membuatnya. Ini bagus untuk menguji ide dengan cepat. |

Desain Sistem-on-Chip (SoC). | Anda menempatkan banyak komponen dalam satu chip. Hal ini membuat chip tersebut kecil dan cepat. Anda dapat melihat hal ini di ponsel dan perangkat pintar. |

Desain Siap Pakai | Anda menggunakan komponen yang sudah teruji dan siap pakai. Proses ini cepat dan efektif untuk banyak produk. |

Tips: Pilih arsitektur yang sesuai dengan kebutuhan proyek Anda. Pertimbangkan kecepatan, daya, dan waktu yang Anda miliki.

Pilihan arsitektur Anda memengaruhi seberapa banyak daya yang digunakan chip Anda dan seberapa cepat kinerjanya. Anda dapat menggunakan trik khusus untuk menghemat daya dan meningkatkan kecepatan. Berikut beberapa cara untuk melakukannya:

Teknik | Uraian Teknis |

|---|---|

Gunakan Komponen Daya Rendah | Pilih komponen yang menggunakan lebih sedikit energi. Ini akan membantu jika chip Anda menggunakan baterai. |

Gerbang Daya | Matikan bagian-bagian chip saat Anda tidak membutuhkannya. |

Skala Tegangan dan Frekuensi Dinamis (DVFS) | Ubah kecepatan chip dan penggunaan daya berdasarkan apa yang dilakukannya. |

Bersepeda Tugas | Nyalakan sirkuit hanya ketika Anda membutuhkannya. |

Minimalkan Peralihan Sinyal | Kurangi frekuensi perubahan sinyal untuk menghemat energi. |

Optimalkan Kapasitansi Beban | Turunkan beban pada keluaran untuk menggunakan lebih sedikit daya. |

CMOS Multi-Ambang Batas (MTCMOS) | Gunakan berbagai jenis sakelar untuk menghemat daya di area utama. |

Sintesis Sadar Daya | Atur peralatan Anda untuk fokus pada penghematan daya saat Anda membangun chip. |

Gerbang Jam di RTL | Hentikan jam di bagian yang tidak digunakan untuk mengurangi pemborosan energi. |

Bias Tubuh | Ubah tegangan untuk mengurangi kebocoran dan menghemat daya. |

Domain Kekuasaan Hirarkis | Membagi chip menjadi beberapa zona untuk mengendalikan daya dengan lebih baik. |

Penggunaan Teknologi FinFET | Gunakan transistor khusus yang kebocorannya lebih sedikit dan bekerja dengan baik pada daya rendah. |

Diagram Blok

Anda menggambar diagram blok untuk menunjukkan cara kerja chip Anda. Diagram ini menggunakan bentuk-bentuk sederhana untuk menunjukkan setiap bagian chip. Anda menghubungkan bentuk-bentuk ini dengan garis untuk menunjukkan bagaimana data bergerak. Diagram blok yang baik membantu semua orang memahami rencana chip.

Saat Anda membuat diagram blok, Anda harus:

Tampilkan semua bagian utama chip.

Gambarkan garis yang jelas untuk aliran data.

Beri label setiap blok dengan tugasnya.

Buatlah diagram yang sederhana dan mudah dibaca.

Diagram blok yang jelas membantu Anda mendeteksi masalah sejak dini. Diagram ini juga membantu tim Anda mendiskusikan chip dan membuat perubahan sebelum Anda mulai membangunnya.

Desain RTL

Tahap desain RTL adalah tahap di mana Anda menuangkan ide-ide Anda ke dalam kode yang menjelaskan cara kerja chip Anda. Anda menggunakan bahasa pemrograman seperti Verilog atau VHDL untuk menulis kode ini. Anda berfokus pada bagaimana data bergerak dan bagaimana setiap bagian chip berperilaku. Tahap ini penting karena menetapkan aturan tentang bagaimana chip Anda akan beroperasi.

Pengkodean RTL

Anda memulai desain RTL dengan menulis kode yang menunjukkan fungsi setiap blok. Anda belum memikirkan tata letak fisiknya. Anda menjelaskan logika dan bagaimana sinyal mengalir. Anda menggunakan pernyataan sederhana untuk menunjukkan bagaimana chip seharusnya merespons input. Anda memastikan setiap bagian bekerja sama sesuai rencana.

Tips: Tulis kode yang jelas dan sederhana. Gunakan komentar untuk menjelaskan bagian-bagian yang rumit. Ini akan membantu Anda dan tim Anda memahami desainnya nanti.

Anda menghadapi beberapa tantangan selama desain RTL. Berikut tabel yang menunjukkan tantangan paling umum:

Tantangan | Uraian Teknis |

|---|---|

Kompleksitas Desain | Anda harus mengelola desain yang besar. Semakin banyak komponen berarti semakin besar kemungkinan kesalahan dan waktu pengerjaan yang lebih lama. |

Memastikan Ketepatan Desain | Anda perlu memeriksa apakah kode Anda cocok dengan apa yang Anda inginkan agar dilakukan oleh chip tersebut. |

Mengelola Konsumsi Daya | Anda mencari cara untuk menghemat energi sambil menjaga chip berfungsi dengan baik. |

Anda harus memperhatikan tantangan-tantangan ini. Jika tidak, Anda mungkin akan mengalami kesalahan atau chip yang menggunakan terlalu banyak daya.

Verifikasi Fungsional

Setelah menyelesaikan pengkodean RTL, Anda beralih ke verifikasi desain. Anda menguji kode untuk memastikannya berfungsi sesuai harapan. Anda menggunakan testbench dan alat simulasi. Anda memeriksa setiap bagian desain RTL untuk menemukan kesalahan sebelum Anda membangun chip.

Anda menjalankan banyak pengujian untuk memastikan chip merespons dengan benar. Anda mencari bug dan memperbaikinya lebih awal. Verifikasi desain membantu Anda menghindari kesalahan yang merugikan di kemudian hari. Anda mengulangi proses ini hingga Anda yakin bahwa desain rtl Anda sesuai dengan tujuan Anda.

Catatan: Verifikasi desain yang baik menghemat waktu dan uang. Anda dapat mendeteksi masalah sebelum menjadi masalah yang lebih besar.

Anda perlu mengingat bahwa desain RTL merupakan langkah kunci dalam membuat chip yang andal. Pengodean yang cermat dan verifikasi desain yang kuat membantu Anda membangun chip yang berfungsi dengan baik dan memenuhi kebutuhan Anda.

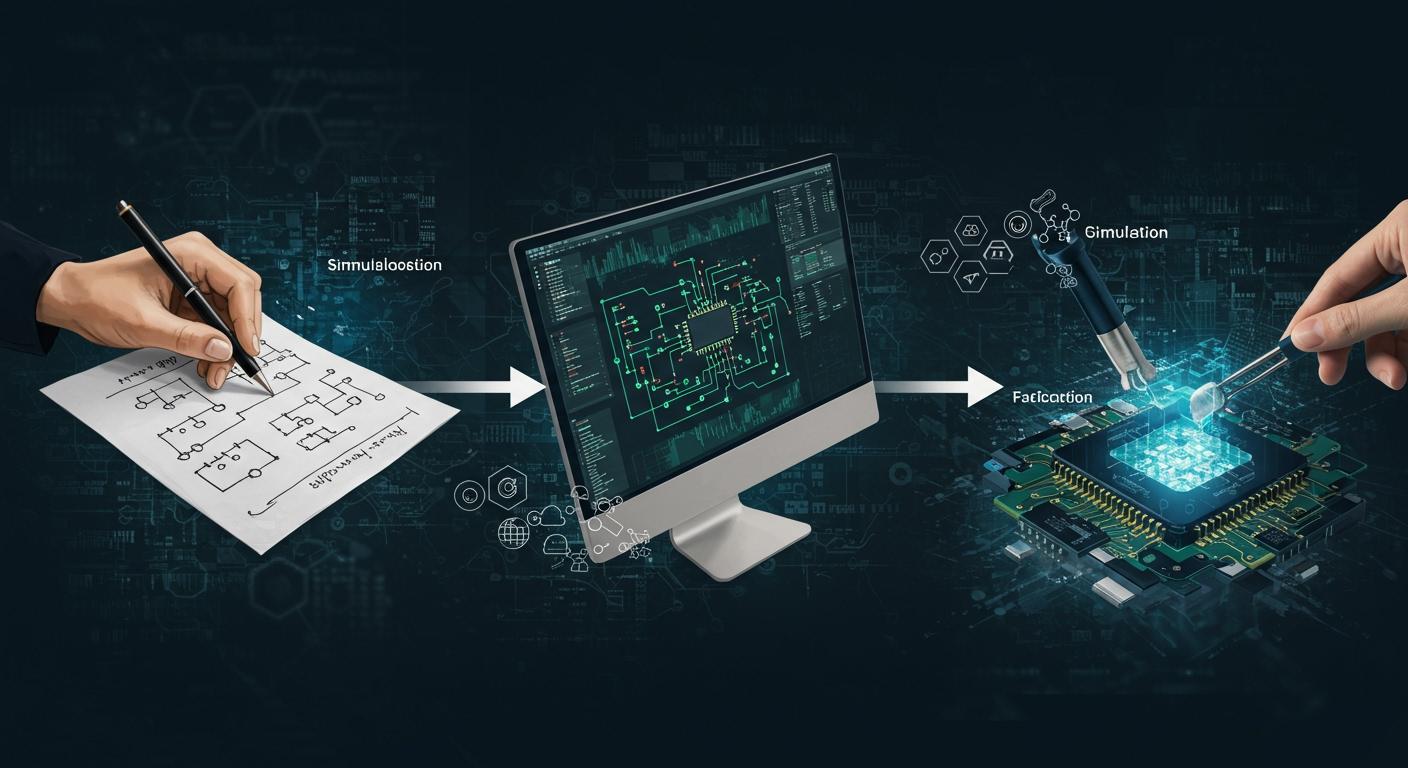

Ikhtisar Alur Desain VLSI

Ketika Anda mulai mempelajari tentang siklus desain VLSI, Anda akan melihat bahwa alur desain vlsi Memberikan Anda alur yang jelas dari sebuah ide hingga chip yang berfungsi. Alur ini membantu Anda menghindari kesalahan dan memastikan desain chip Anda berfungsi sesuai rencana.

Tahapan dalam aliran desain VLSI

Anda akan mengikuti serangkaian langkah dalam alur desain VLSI. Setiap langkah dibangun berdasarkan langkah sebelumnya. Berikut urutan umum yang akan Anda lihat dalam alur tersebut:

Konseptualisasi dan Spesifikasi

Desain arsitektur

Desain Logika

Sintesis RTL

Netlist dan Floorplanning

Penempatan dan Perutean

Verifikasi Fisik

Analisis Waktu

Ekstraksi dan Simulasi

Rekaman

Kegiatan utama

Anda akan menyadari bahwa setiap tahap dalam alur memiliki tugas khusus. Alur desain VLSI dimulai dengan rencana yang jelas dan diakhiri dengan chip yang nyata. Anda memeriksa pekerjaan Anda di setiap langkah. Ini membantu Anda menemukan masalah sejak dini. Anda dapat memperbaikinya sebelum masalah tersebut berkembang. Alurnya meliputi langkah-langkah seperti spesifikasi, entri desain, sintesis, verifikasi, tata letak, dan fabrikasi. Masing-masing membantu Anda memastikan desain chip Anda benar. Siklus cermat ini menjaga kesalahan tetap rendah dan kualitas tetap tinggi.

Anda akan melihat bahwa alur adalah panduan Anda untuk setiap proyek VLSI. Dengan mengikuti alur, Anda akan membuat desain chip Anda kuat dan andal. Alur adalah tulang punggung setiap chip VLSI yang sukses.

Sintesis Logika

RTL ke Gates

Sintesis logika adalah langkah kunci dalam mewujudkan ide Anda menjadi perangkat keras nyata. Pada tahap ini, Anda mengambil kode RTL dan mengubahnya menjadi gerbang logika. Anda menggunakan alat khusus untuk melakukan pekerjaan ini. Alat-alat ini membaca kode RTL Anda dan menciptakan jaringan gerbang yang dapat dibangun di dalam sebuah chip.

Anda akan melihat tiga langkah utama dalam sintesis logika:

Terjemahan: Alat ini mengubah kode RTL Anda menjadi bentuk yang menggunakan persamaan Boolean. Langkah ini tidak bergantung pada teknologi chip.

Optimasi: Alat ini menyederhanakan persamaan Boolean. Alat ini menggunakan metode seperti jumlah produk untuk melakukan hal ini.

Pemetaan Teknologi: Alat ini mencocokkan persamaan yang dioptimalkan dengan gerbang asli dari pustaka. Alat ini memilih gerbang yang sesuai dengan kebutuhan desain Anda.

Tips: Selalu periksa kode RTL Anda untuk menemukan kesalahan sebelum memulai sintesis. Kode yang bersih membantu Anda mendapatkan hasil yang lebih baik.

Optimization

Optimasi membantu Anda mendapatkan chip terbaik untuk kebutuhan Anda. Anda ingin chip Anda berukuran kecil, cepat, dan hemat daya. Alat sintesis logika membantu Anda mencapai tujuan ini dengan membuat pilihan cerdas selama proses berlangsung.

Berikut adalah tabel yang menunjukkan bagaimana pengoptimalan memengaruhi chip Anda:

Aspek | Dampak pada Chip VLSI |

|---|---|

Optimasi Area | Mengurangi jejak fisik, memungkinkan lebih banyak chip pada wafer, yang menghasilkan hasil lebih tinggi dan biaya lebih rendah. |

Optimalisasi Kecepatan | Jaringan yang lebih cepat sering kali mengakibatkan konsumsi area yang lebih besar, sehingga memerlukan keseimbangan antara kecepatan dan area. |

Konsumsi Energi | Gerbang yang lebih besar meningkatkan kapasitansi, menyebabkan konsumsi energi lebih tinggi selama peralihan. |

Anda perlu menyeimbangkan area, kecepatan, dan penggunaan energi. Jika Anda membuat chip Anda lebih cepat, ukurannya mungkin akan lebih besar dan menggunakan lebih banyak daya. Jika Anda membuatnya lebih kecil, kinerjanya mungkin akan lebih lambat. Sintesis logika yang baik akan membantu Anda menemukan keseimbangan terbaik.

Optimalisasi area memungkinkan Anda memasang lebih banyak chip pada satu wafer. Ini mengurangi biaya dan memungkinkan Anda menambahkan lebih banyak fitur.

Optimalisasi kecepatan membuat chip Anda bekerja lebih cepat, tetapi dapat menggunakan lebih banyak ruang dan energi.

Penggunaan ruang yang efisien penting untuk menambahkan fungsi baru tanpa mengganggu kinerja.

Anda menggunakan sintesis logika di setiap proyek VLSI. Sintesis logika ini membentuk desain Anda dan membantu Anda membangun chip yang berfungsi dengan baik di dunia nyata.

Desain Fisik

The tahap desain fisik Di sinilah Anda mengubah logika chip Anda menjadi tata letak yang nyata. Anda memutuskan di mana setiap bagian chip akan ditempatkan dan bagaimana kabel akan menghubungkannya. Langkah ini penting dalam desain fisik VLSI karena menentukan seberapa baik kinerja chip Anda dan apakah chip tersebut dapat dibuat tanpa masalah.

Perencanaan Lantai

Tahap desain fisik dimulai dengan perencanaan lantai. Di sini, Anda membagi chip menjadi blok-blok dan memberi setiap blok ruangnya sendiri. Anda memikirkan seberapa besar ukuran setiap blok dan di mana akan meletakkannya. Perencanaan lantai yang baik membantu Anda menghindari area yang ramai dan memastikan sinyal dapat terpancar dengan cepat. Anda juga merencanakan ruang untuk saluran listrik dan jam. Langkah ini menentukan struktur untuk proses desain fisik VLSI selanjutnya.

Banyak alat yang membantu Anda dalam perencanaan lantai dan tugas lainnya pada tahap ini. Beberapa alat yang paling populer meliputi::

Synopsys IC Compiler II: Tempat dan rute cepat, desain sadar daya.

Mentor Graphics Calibre: Memeriksa aturan dan mencocokkan tata letak dengan skema.

ANSYS RedHawk: Memeriksa daya dan keandalan.

Tanner Tools: Baik untuk tata letak analog dan sinyal campuran.

Avanti Hercules: Memeriksa integritas sinyal dan daya.

OpenROAD: Alat sumber terbuka untuk desain fisik.

KLATencor L-Edit: Digunakan untuk tata letak IC khusus.

Kiat: Pilih alat yang sesuai dengan kebutuhan proyek dan keterampilan tim Anda.

Penempatan & Perutean

Setelah perencanaan lantai, Anda beralih ke penempatan dan perutean. Anda menempatkan setiap sel atau blok pada tempatnya. Anda ingin menjaga blok-blok terkait tetap berdekatan. Ini membantu sinyal bergerak lebih cepat dan menghemat daya. Anda juga memastikan chip tidak terlalu panas.

Selanjutnya, Anda akan merutekan kabel. Anda akan menggambar jalur bagi sinyal untuk bergerak di antara blok. Anda akan menyeimbangkan kecepatan dan menghindari jalur yang ramai. Anda juga akan memeriksa apakah tata letak Anda mengikuti aturan pembuatan chip. Langkah-langkah ini akan membantu chip Anda berfungsi dengan baik dan memudahkan proses produksi.

Anda mengikuti langkah-langkah utama berikut dalam tahap desain fisik:

Mempartisi dan menata denah chip.

Tempatkan sel dan blok.

Bangun pohon jam.

Rutekan kabelnya.

Periksa aturan dan kemampuan produksi.

Optimalkan daya.

Setelah Anda menyelesaikan tahap desain fisik, Anda memiliki tata letak yang siap untuk diproduksi. Langkah ini kunci untuk setiap proyek vlsi.

Desain untuk Testabilitas

Saat Anda bekerja pada chip VLSI, Anda ingin memastikan Anda dapat mengujinya dengan mudah. Desain untuk kemampuan uji membantu Anda menemukan masalah lebih awal dan memperbaikinya sebelum chip mencapai pelanggan. Anda menambahkan fitur-fitur khusus ke chip Anda sehingga Anda dapat memeriksa apakah semuanya berfungsi sesuai rencana. Fitur-fitur ini mempercepat pengujian dan membantu Anda menghemat biaya selama produksi.

Fitur Tes

Anda menggunakan beberapa teknik untuk meningkatkan kemampuan uji pada chip Anda. Metode-metode ini membantu Anda mendeteksi kesalahan dan memastikan chip Anda berfungsi dengan baik.

Desain pemindaian memungkinkan Anda mengontrol dan memeriksa flip-flop di dalam chip selama pengujian.

Pemindaian batas membantu Anda menguji koneksi antara chip pada papan tanpa menggunakan probe.

Built-In Self-Test (BIST) menambahkan perangkat keras pengujian di dalam chip sehingga dapat menguji dirinya sendiri.

Memory BIST (MBIST) memeriksa blok memori di dalam chip Anda.

ATPG (Pembuatan Pola Uji Otomatis) menciptakan pola yang membantu Anda menemukan kesalahan setelah produksi.

Fitur-fitur ini meningkatkan cakupan pengujian dan mengurangi waktu yang dibutuhkan untuk pengujian. Anda dapat menemukan kesalahan dengan cepat dan menghindari pengiriman chip yang rusak kepada pelanggan.

olymp trade indonesiaTip: Tambahkan fitur pengujian lebih awal dalam proses desain Anda. Hal ini memudahkan pengujian dan menurunkan biaya.

Anda akan melihat banyak manfaat ketika menggunakan teknik-teknik ini. Tabel di bawah ini menunjukkan bagaimana desain untuk uji coba membantu chip Anda:

Manfaat | Uraian Teknis |

|---|---|

Deteksi kesalahan | |

Peningkatan Hasil Produksi | Anda memperbaiki masalah selama produksi dan mendapatkan lebih banyak chip yang bagus. |

Keandalan | Anda memastikan chip Anda bekerja dengan baik untuk waktu yang lama. |

Anda dapat menguji chip yang kompleks dengan lebih cepat dan akurat. Anda menghasilkan chip berkualitas tinggi yang berfungsi sesuai harapan.

Rantai Pemindaian

Rantai pemindaian berperan penting dalam pengujian chip VLSI. Anda menghubungkan flip-flop dalam sebuah rantai sehingga Anda dapat mengatur dan membaca nilainya selama pengujian. Pengaturan ini memungkinkan Anda memeriksa bagian dalam chip tanpa membongkarnya.

Anda menggunakan rantai pemindaian untuk menemukan kesalahan pada blok logika. Anda mengontrol setiap flip-flop dan mengamati bagaimana sinyal bergerak melalui chip Anda. Metode ini membantu Anda menemukan masalah yang mungkin terlewatkan oleh pengujian normal.

Dengan menambahkan rantai pemindaian, Anda membuat chip Anda lebih mudah diuji dan lebih andal. Anda juga mengurangi risiko kegagalan yang merugikan setelah chip Anda terpasang di produk.

Catatan: Jika Anda merencanakan rantai pemindaian dengan baik, Anda dapat menghemat waktu dan meningkatkan kualitas chip Anda.

Mengintegrasikan desain untuk pengujian lebih awal membantu Anda mengurangi waktu pengujian dan menghindari kesalahan mahal. Anda membangun chip yang lebih awet dan berkinerja lebih baik.

Analisis Waktu

Analisis timing membantu Anda memastikan chip Anda bekerja dengan kecepatan yang tepat. Langkah ini digunakan untuk memeriksa apakah sinyal bergerak melalui chip Anda cukup cepat. Jika Anda melewatkan analisis timing, chip Anda mungkin tidak berfungsi sesuai rencana. Dalam VLSI, analisis timing merupakan salah satu pemeriksaan terpenting sebelum Anda menyelesaikan desain.

Pengaturan Waktu Statis

Kau gunakan analisis waktu statis (STA) untuk memeriksa pengaturan waktu chip Anda tanpa menjalankan pola uji. STA memeriksa setiap jalur di sirkuit Anda dan memeriksa apakah sinyal tiba tepat waktu. Metode ini membantu Anda menemukan masalah lebih awal. Anda tidak perlu menggunakan vektor input, sehingga Anda dapat memeriksa semua kemungkinan jalur dengan cepat.

Berikut adalah beberapa metode analisis waktu umum Anda mungkin menggunakan:

Analisis Waktu Statis (STA)

Analisis Waktu Dinamis (DTA)

Analisis Waktu Statis Statistik (SSTA)

Analisis waktu penandatanganan

Analisis multi-sudut dan multi-mode (MCMM)

Analisis variasi pada chip (OCV)

STA berperan penting dalam mencegah pelanggaran waktu. Anda ingin sinyal mencapai flip-flop dan register pada saat yang tepat. Jika sinyal datang terlalu lambat atau terlalu cepat, chip Anda bisa rusak. Lebih dari 80% kegagalan desain pada silikon terjadi karena pelanggaran waktu. STA membantu Anda menghindari kesalahan mahal ini.

Catatan: Analisis waktu statis memeriksa kecepatan maksimum chip Anda dan memastikan semua sinyal tiba tepat waktu. Langkah ini penting agar chip berfungsi dengan baik.

Penutupan Waktu

Penutupan waktu adalah proses untuk memperbaiki semua masalah pengaturan waktu pada chip Anda. Anda ingin setiap sinyal memenuhi target pengaturan waktunya. Anda mungkin perlu mengubah desain, memindahkan blok, atau menyesuaikan panjang kabel. Penutupan waktu memang membutuhkan banyak upaya, tetapi sangat penting agar chip berfungsi dengan baik.

Anda mengikuti langkah-langkah berikut untuk mencapai penutupan waktu:

Menganalisis laporan waktu dari STA.

Temukan jalur yang gagal dalam pengaturan waktu.

Ubah desain Anda untuk memperbaiki jalur ini.

Jalankan STA lagi untuk memeriksa apakah Anda telah memperbaiki masalahnya.

Ulangi hingga Anda mencapai waktu penutupan.

Anda dapat menggunakan alat khusus untuk membantu pengaturan waktu penutupan. Alat ini menunjukkan jalur mana yang perlu diperbaiki. Anda dapat mengubah desain dan melihat hasilnya dengan cepat. Pengaturan waktu penutupan memastikan chip Anda bekerja dengan kecepatan yang Anda inginkan.

Tips: Mulailah bekerja pada penutupan waktu lebih awal. Memperbaiki masalah waktu pada akhirnya bisa sangat sulit.

Anda memerlukan penutupan waktu sebelum dapat menyelesaikan desain VLSI Anda. Langkah ini memberi Anda keyakinan bahwa chip Anda akan berfungsi di dunia nyata.

Verifikasi Fisik

Pemeriksaan verifikasi fisik Jika tata letak chip Anda siap dibuat, Anda perlu memastikan chip Anda berfungsi dan mengikuti semua aturan pengecoran. Langkah ini membantu Anda menemukan kesalahan sebelum membuat chip. Anda menggunakan berbagai pemeriksaan untuk memastikan tata letak Anda aman dan benar.

Berikut adalah tabel yang mencantumkan langkah-langkah utama dalam verifikasi fisik dan apa yang mereka lakukan:

Langkah Verifikasi | Tujuan |

|---|---|

Pemeriksaan Aturan Desain (DRC) | Memeriksa apakah tata letak mengikuti aturan pengecoran untuk lebar dan jarak. |

Tata Letak vs Skema (LVS) | Memastikan tata letak sesuai dengan rencana rangkaian, atau skema. |

Pemeriksaan Aturan Listrik (ERC) | Menemukan masalah kelistrikan seperti kabel yang hilang atau kapasitansi yang terlalu besar. |

DRC

Anda memulai dengan Pemeriksaan Aturan Desain, yang disebut DRC. Pemeriksaan ini memeriksa tata letak chip Anda dan membandingkannya dengan aturan pabrik pengecoran. Aturan ini menentukan seberapa lebar dan seberapa jauh jarak antar kabel. Jika Anda melanggar aturan ini, chip Anda mungkin tidak berfungsi atau sulit dibuat.

DRC adalah bagian dari verifikasi fisikAlat ini membantu Anda menemukan masalah seperti kabel yang terlalu rapat atau bentuk yang terlalu kecil. Memperbaiki masalah ini akan membuat chip Anda lebih mudah dirakit dan lebih andal.

Proses | Fokus | Tujuan |

|---|---|---|

DRC | Verifikasi Fisik | Memastikan chip dapat dibuat dengan mengikuti aturan desain. |

Tips: Selalu jalankan DRC sebelum Anda menyelesaikan tata letak. Langkah ini menghemat waktu dan biaya.

LVS

Setelah DRC, Anda melakukan Layout vs Schematic, atau LVS. Pemeriksaan ini memastikan tata letak Anda sesuai dengan rencana rangkaian Anda. Anda ingin setiap kabel dan komponen dalam tata letak Anda sesuai dengan skema Anda.

LVS adalah tentang verifikasi kelistrikan. Sistem ini memeriksa apakah chip Anda akan berfungsi sesuai rencana. Jika LVS menemukan kesalahan, Anda perlu memperbaikinya sebelum melanjutkan.

Proses | Fokus | Tujuan |

|---|---|---|

LVS | Verifikasi Listrik | Memastikan tata letak sesuai dengan skema untuk pekerjaan yang benar. |

Verifikasi fisik merupakan bagian penting dari proses VLSI. Dengan menggunakan DRC dan LVS, Anda memastikan desain Anda tepat dan siap untuk langkah selanjutnya.

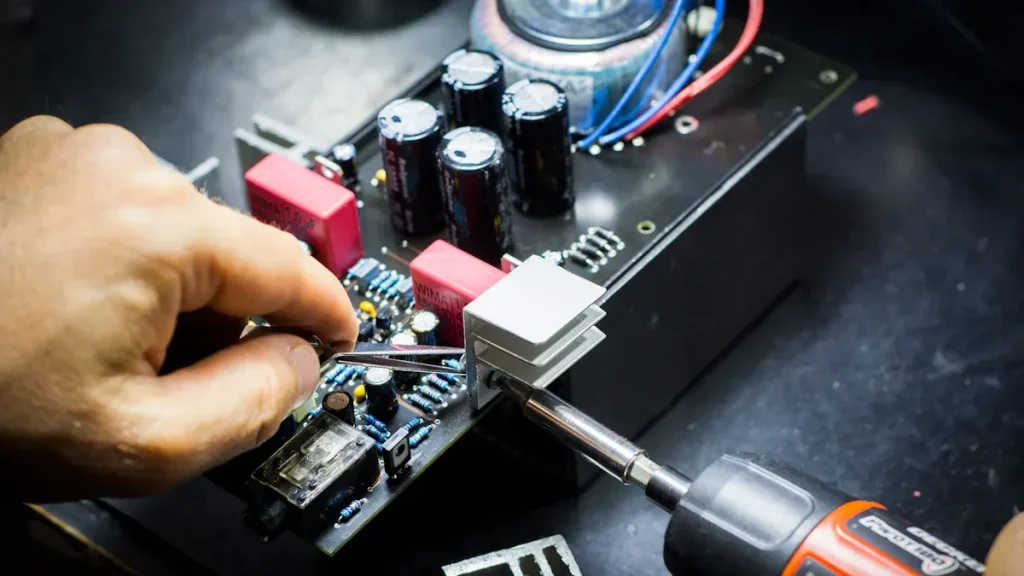

pabrik

Setelah Anda menyelesaikan tapeout dalam siklus desain VLSI, Anda mulai pembuatanLangkah ini mewujudkan desain chip Anda. Ide Anda berubah menjadi chip silikon. Chip ini digunakan untuk ponsel, komputer, dan perangkat lainnya.

Pengolahan Wafer

Pemrosesan wafer Ini adalah bagian pertama dari pembuatan chip. Anda menggunakan sepotong silikon tipis yang disebut wafer. Anda mengikuti banyak langkah untuk membangun lapisan dan sirkuit di atasnya. Setiap langkah menambahkan sesuatu yang penting ke chip Anda.

Berikut adalah langkah-langkah utama pemrosesan wafer:

Membersihkan permukaan

Anda membersihkan wafer untuk menghilangkan debu.Oksidasi Awal

Anda menumbuhkan lapisan oksida tipis pada wafer.Deposisi CVD

Anda menaruh material baru pada wafer dengan gas khusus.Pelapis Photoresist

Anda melapisi wafer dengan bahan yang bereaksi terhadap cahaya.Metalisasi dan Interkoneksi

Anda menambahkan logam untuk menghubungkan bagian-bagian chip.Poles Mekanik Kimia (CMP)

Anda memoles wafer untuk membuatnya rata dan halus.Pengujian dan Pengemasan Akhir

Anda menguji chip dan menyiapkannya untuk dikemas.

Anda dapat mengulangi beberapa langkah untuk membuat chip yang kompleks. Setiap tahap membantu Anda membangun chip yang sesuai dengan rencana Anda.

Kiat: Pemrosesan wafer yang cermat menghentikan cacat dan menghasilkan chip yang lebih baik.

Tangga Pengecoran

Setelah pemrosesan wafer, Anda mengirimkan chip Anda ke pabrik pengecoran untuk tapeout. Setiap pabrik pengecoran menggunakan metode pembuatan chip yang berbeda. Mereka memiliki gaya bisnis, teknologi, dan tujuan penelitian yang berbeda.

Berikut adalah tabel yang menunjukkan apa yang dilakukan oleh produsen terkemuka:

Pabrikan | Model Bisnis | Fokus Node Proses | Fokus R&D |

|---|---|---|---|

TSMC | Pengecoran murni | Node proses yang lebih kecil | Meningkatkan node proses dan meningkatkan hasil |

Intel | Integrasi vertikal | Mendapatkan kembali pimpinan teknologi | Kemasan baru, chip AI, komputasi kuantum |

Samsung | Pengecoran dan chip memori | Node tingkat lanjut | Ide-ide baru dalam memori dan chip logika |

Pilihlah pabrik pengecoran yang sesuai dengan kebutuhan Anda. Beberapa pabrik pengecoran menghasilkan serpihan yang lebih kecil dan lebih cepat. Pabrik pengecoran lainnya mengerjakan kemasan baru atau fitur-fitur khusus. Langkah tapeout Anda bergantung pada keahlian terbaik pabrik pengecoran tersebut.

Fabrikasi merupakan bagian yang sangat penting dari siklus desain VLSI. Anda harus mengikuti setiap langkah untuk mendapatkan chip yang baik setelah tapeout.

Pengujian & Pengemasan

Pengujian Listrik

Anda harus memeriksa setiap chip sebelum meninggalkan pabrik. Pengujian kelistrikan memastikan chip Anda berfungsi sesuai rencana. Langkah ini membantu Anda menemukan masalah dalam pembuatan chip. Ada beberapa cara untuk menguji chip. Beberapa cara yang umum adalah:

Pemodelan kesalahan

Pembuatan Pola Uji Otomatis (ATPG)

Pengujian pemindaian batas (JTAG)

Pengujian fungsional

Pengujian parametrik

DFT memungkinkan Anda menambahkan fitur-fitur khusus saat merancang chip. Fitur-fitur ini memudahkan pengujian. Built-In Self-Test (BIST) memungkinkan chip menguji dirinya sendiri. Anda tidak memerlukan alat tambahan untuk ini. ATPG membuat pola pengujian untuk menemukan kesalahan dengan cepat. Metode ini membantu Anda menghemat uang dan waktu. Anda dapat memperbaiki masalah sebelum pelanggan menerima chip. Pengujian yang baik berarti hanya chip yang berfungsi yang diberikan kepada pengguna. Hal ini membuat pengguna senang.

Tips: Pengujian kelistrikan membantu Anda mendeteksi kerusakan lebih awal. Ini memastikan chip VLSI Anda berfungsi dengan baik.

Metode Pengemasan

Setelah pengujian, Anda harus melindungi chip dan menghubungkannya. Pengemasan akan melakukan tugas ini untuk Anda. Cara Anda mengemas chip memengaruhi kinerjanya. Pengemasan juga memengaruhi daya tahannya. Anda perlu mempertimbangkan panas, daya, dan sinyal.

Teknologi interkoneksi penting dalam pengemasan. Benjolan mikro, vias silikon tembus (TSV), dan lapisan redistribusi (RDL) membantu menghubungkan chip. Mikro-benjolan baik untuk sambungan chip-ke-substrat. Namun, mikro-benjolan ini dapat menimbulkan masalah dengan panas dan guncangan. Elektromigrasi dan migrasi termal dapat mengganggu keandalan.

TSV memungkinkan sinyal dan panas bergerak naik turun di dalam chip. Hal ini membantu chip bekerja lebih baik. Namun, material yang berbeda dapat retak atau pecah ketika chip menjadi panas atau dingin.

Untuk membuat kemasan yang lebih baik, Anda harus mempelajari panas, listrik, dan gaya. Penggunaan material baru seperti interkoneksi berdensitas tinggi dan material termal canggih membantu mengendalikan panas. Hal ini juga membuat kemasan lebih awet. Seiring kemasan menjadi lebih cepat dan kecil, desain kemasan yang baik menjadi semakin penting.

Anda bisa melihatnya pengujian dan pengemasan Keduanya penting. Keduanya membantu chip Anda berfungsi dengan baik dan tahan lama.

Validasi Silikon

Setelah selesai membuat chip, Anda perlu memeriksa apakah chip tersebut berfungsi sesuai rencana. Langkah ini disebut validasi silikon. Anda ingin memastikan chip Anda sesuai dengan desain asli dan berfungsi dengan baik di dunia nyata.

Pemeriksaan Pasca-Fabrikasi

Setelah fabrikasi, Anda menguji chip pertama yang datang dari pabrik. Chip ini disebut prototipe. Anda menempatkannya pada papan khusus dan menjalankan banyak pengujian. Anda mencari masalah yang tidak terdeteksi selama pemeriksaan sebelumnya. Terkadang, bug lolos dari putaran pengujian pertama. Sekarang, Anda dapat menemukannya karena chip berjalan pada kecepatan sistem yang sebenarnya.

Anda mengikuti proses standar untuk validasi silikon:

Verifikasi pra-silikon Menggunakan perangkat lunak untuk menguji chip Anda sebelum diproduksi. Anda menjalankan kasus uji dalam simulator. Langkah ini memeriksa apakah kode RTL Anda sesuai dengan spesifikasi.

Validasi pasca-silikon dimulai setelah Anda mendapatkan chip asli. Anda menguji chip tersebut pada perangkat keras. Anda melihat cara kerjanya secara langsung dan dalam kondisi nyata.

Catatan: Validasi pasca-silikon membantu Anda menemukan masalah yang hanya muncul saat chip berjalan pada kecepatan penuh atau di lingkungan nyata.

Produk akhir

Setelah semua pemeriksaan selesai, Anda akan tahu apakah chip Anda siap dipasarkan. Anda akan melihat kinerja chip, seberapa banyak daya yang digunakan, dan apakah chip tersebut memenuhi semua target Anda. Jika menemukan masalah, Anda dapat memperbaikinya sebelum memproduksi lebih banyak chip.

Berikut adalah tabel sederhana untuk menunjukkan perbedaan antara langkah pra-silikon dan pasca-silikon:

Langkah | Ketika Itu Terjadi | Apa yang Anda Uji | Kecepatan Pengujian |

|---|---|---|---|

Verifikasi Pra-silikon | Sebelum fabrikasi | Simulator perangkat lunak | Bukan kecepatan sistem yang sebenarnya |

Validasi Pasca-silikon | Setelah fabrikasi | Perangkat keras nyata | Kecepatan sistem nyata |

Anda memerlukan validasi silikon untuk memastikan chip VLSI Anda berfungsi sesuai rencana. Langkah ini memberi Anda keyakinan bahwa desain Anda akan berhasil di dunia nyata.

Anda membuat desain chip VLSI lebih andal dengan mengikuti setiap tahapan. Dengan demikian, Anda dapat menghindari kesalahan dan menjaga pekerjaan Anda tetap stabil. Mengetahui alur desain VLSI membantu Anda meningkatkan kecepatan, ukuran, dan penggunaan daya. Hal-hal baru seperti Otomatisasi berbasis AI dan integrasi 3D mengubah masa depan VLSI. Jika Anda ingin berkembang dalam pekerjaan Anda, pelajari keterampilan baru, dapatkan sertifikat, dan berdiskusi dengan para ahli. Siklus ini membantu Anda membangun chip yang lebih baik dan tetap terdepan di bidang teknologi.

kecenderungan | Dampak pada Teknologi Semikonduktor |

|---|---|

Otomatisasi desain berbasis AI | Membuat desain chip lebih cepat dan mudah |

Strategi optimasi daya | Membantu perangkat kecil bekerja lebih baik |

Teknik integrasi 3D | Memberikan kontrol kecepatan dan panas yang lebih baik |

Pendekatan yang mengutamakan keamanan | Menjaga chip tetap aman dari peretas |

Alat simulasi tingkat lanjut | Memeriksa desain lebih cepat dan lebih akurat |

Periksa apa yang Anda ketahui dan perbaiki titik lemahnya.

Ikuti kelas khusus.

Bertemu dan berbicara dengan orang-orang di lapangan.

FAQ (Pertanyaan Umum)

Apa itu siklus desain VLSI?

Anda mengikuti siklus desain VLSI untuk membuat chip langkah demi langkah. Siklus ini membantu Anda merencanakan, membangun, dan menguji chip Anda. Setiap tahap memastikan chip Anda berfungsi dengan baik dan memenuhi kebutuhan Anda.

Mengapa VLSI penting dalam elektronika?

Anda menggunakan VLSI untuk memasukkan jutaan komponen kecil ke dalam satu chip. Hal ini membuat perangkat lebih kecil, lebih cepat, dan lebih pintar. Ponsel, komputer, dan mobil semuanya menggunakan chip VLSI agar berfungsi lebih baik.

Bagaimana Anda memulai proyek desain?

Mulailah dengan menuliskan apa yang Anda inginkan dari chip Anda. Tetapkan tujuan yang jelas dan daftarkan fitur-fiturnya. Ini membantu Anda dan tim tetap fokus dan menghindari kesalahan.

Alat apa yang membantu desain VLSI?

Kau gunakan perangkat lunak khusus untuk menggambar, uji, dan periksa chip Anda. Alat seperti Synopsys, Mentor Graphics, dan Cadence membantu Anda merancang, mensimulasikan, dan memverifikasi chip Anda sebelum membuatnya.

Bisakah Anda memperbaiki kesalahan setelah membuat chip?

Anda dapat menemukan dan memperbaiki beberapa kesalahan selama pengujian. Jika menemukan masalah besar, Anda mungkin perlu mengubah desain dan membuat chip baru. Perencanaan yang cermat membantu Anda menghindari kesalahan yang merugikan.