La integritat del senyal és molt important en el disseny ràpid de PCB. Sense ella, els senyals es poden debilitar, causant errors i un mal rendiment. Es poden produir problemes com ara interferències electromagnètiques (EMI), desajustos d'impedància i retards. Per exemple:

Les proves mostren que els VIA penjats poden actuar com a petits condensadors o antenes, cosa que empitjora l'EMI.

Les traces que no estiguin alineades amb el teixit de fibra de vidre poden canviar la impedància i distorsionar els senyals.

Per solucionar aquests problemes, podeu millorar el disseny de traçat en el disseny del vostre PCB, triar millors materials i controlar bé les EMI.

Sortides de claus

La força del senyal és molt important per a PCB ràpides. Manté els senyals clars i evita errors o problemes.

Trieu materials amb una constant dielèctrica i una tangent de pèrdues baixes. Això ajuda a mantenir els senyals forts i millora el rendiment.

Feu traçats curts i eviteu girs pronunciats en el ruteig. Això redueix la pèrdua de senyal i les interferències (EMI).

Utilitzeu parells diferencials per mantenir els senyals equilibrats i reduir el soroll. La coincidència de les longituds i l'espaiat de les traces ajuda a mantenir els senyals clars.

Afegiu blindatge i connexió a terra per reduir les EMI. Els plans de terra i les cobertes metàl·liques protegeixen les peces i milloren la qualitat del senyal.

Comprensió de la integritat del senyal en el disseny de PCB d'alta velocitat

Què és la integritat del senyal?

La integritat del senyal significa mantenir un senyal fort i clar a mesura que es mou a través d'una placa de circuit imprès ràpida. A velocitats de fins a 4 GHz, les connexions actuen com a línies de transmissió. Això pot causar problemes com ara soroll, retards i canvis de senyal. La integritat del senyal és important per mantenir els senyals nets i puntuals per a un bon rendiment.

Per mantenir els senyals forts, cal solucionar problemes com les reflexions, la diafonia i les EMI. Les proves i les simulacions ajuden a trobar i resoldre aquests problemes. Estàndards com l'IEEE 802.3ap estableixen regles per garantir que les plaques de circuit imprès d'alta velocitat funcionin de la mateixa manera.

Aspecte | Que significa |

|---|---|

Per què importen les simulacions | Ajuden a crear regles per a connectors ràpids. |

Problemes d'integritat del senyal | Els problemes inclouen reflexions, diafonia i debilitament del senyal. |

Fer regles | Grups com PICMG i OBSAI creen estàndards d'integritat del senyal. |

Normes de l'IEEE | Estableix límits de rendiment dels canals. |

Problemes en dissenys de PCB d'alta velocitat

Els dissenys ràpids de PCB tenen molts problemes que perjudiquen la qualitat del senyal:

La diafonia es produeix quan els senyals en camins propers es confonen entre si.

Els desajustos d'impedància provoquen senyals rebotar, cometent errors.

Un mal encaminament sobre plans dividits empitjora el soroll i les EMI.

Els errors de soldadura, com ara les llacunes en les connexions, debiliten els senyals.

Aquests problemes poden fer que la teva placa de circuit implícit funcioni malament. Per exemple, les esquerdes en vies petites o els canvis en les propietats del material poden alterar els senyals. Per solucionar-ho, utilitza mètodes com la senyalització diferencial, les terminacions adequades i les traces de guarda.

Com la mala integritat del senyal perjudica el rendiment

Una mala integritat del senyal pot fer que la placa de circuit imprès funcioni malament. Els senyals poden perdre la seva forma, fent que els dispositius els llegeixin incorrectament. Els desajustos d'impedància i l'afebliment d'alta freqüència redueixen la intensitat del senyal, provocant velocitats més lentes i errors.

El soroll addicional, com ara el jitter o els canvis de voltatge, altera la sincronització del senyal. El rebot de terra pot canviar els nivells de voltatge i provocar errors. La diafonia afegeix senyals no desitjats als camins propers, fent que les dades siguin menys precises.

Per evitar aquests problemes, feu servir un pla de referència estable per a senyals ràpids. Això redueix el soroll i les interferències electromagnètiques (EMI), mantenint els senyals clars. La solució d'aquests problemes fa que la vostra placa de circuit imprès (PCB) sigui més fiable i tingui un millor rendiment.

Estratègies clau per al disseny de PCB d'alta velocitat

Selecció de materials per a la integritat del senyal

Triar els materials adequats és clau per mantenir els senyals forts. Els materials que utilitzeu afecten la manera com es mouen els senyals a través de la PCB. Materials amb baixa constant dielèctrica (Dk) i tangent de pèrdues (Df) ajuden a mantenir els senyals clars i forts.

Propietat | Recomanació |

|---|---|

Constant dielèctrica (Dk) | Trieu materials amb baixes Df (<0.005) per a ús de RF i microones. |

Coeficient de dilatació tèrmica (CTE) | Utilitzeu laminats amb baixes CTE (10 a 20 ppm/°C) per a una millor estabilitat. |

Gruix del substrat | Trieu substrats més prims (de 10 a 20 mil·límetres) per a altes freqüències per sobre dels 10 GHz. |

Tangent de pèrdua | Seleccioneu materials amb tangents de baixa pèrdua (0.0022 a 0.0095) per reduir la pèrdua de senyal. |

Absorció d’humitat | Trieu materials amb baixa absorció d'humitat (<0.1%) per a un millor rendiment. |

Reviseu atentament les dades del material. Les proves mostren que el real Df els valors poden diferir del que indiquen els proveïdors. Fins i tot una petita diferència, com ara 0.004 en Df, pot augmentar la pèrdua de senyal. Provar els materials abans de dissenyar la PCB ajuda a evitar aquests problemes.

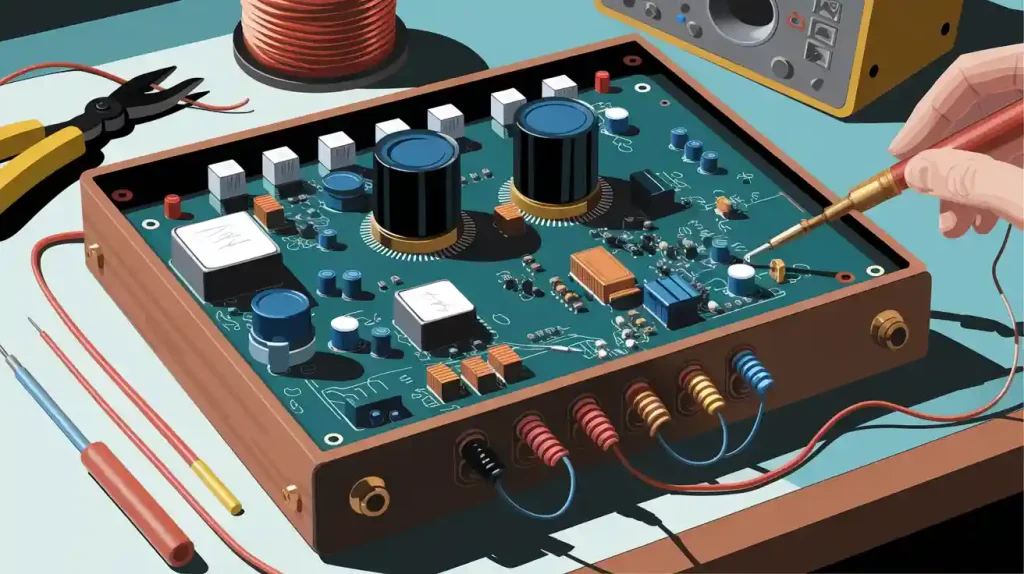

Millors pràctiques de disseny de traça i enrutament

Un bon disseny i encaminament de les pistes són importants per a les PCB ràpides. Les pistes més curtes mantenen els senyals forts i redueixen els efectes no desitjats. La impedància controlada garanteix que les pistes coincideixin amb les parts connectades, mantenint els senyals clars.

Millors pràctiques | Explicació |

|---|---|

Mantingueu els traços curts | Els traços curts redueixen la possibilitat de pèrdua de senyal i efectes no desitjats. |

Utilitza impedància controlada | Coincideix amb la impedància de traça per reduir les reflexions del senyal i mantenir els senyals clars. |

Ruta amb cura | Eviteu les cantonades afilades i limiteu les vies per reduir la pèrdua de senyal i la diafonia. |

Eviteu les cantonades afilades en el traçat de traçats. Les cantonades afilades poden causar reflexions del senyal i més. EMIFeu servir corbes suaus o angles de 45 graus. Limiteu les vies perquè afegeixen efectes no desitjats que debiliten els senyals. Eines com Altium Designer i Cadence us poden ajudar a millorar l'encaminament de la vostra PCB.

Aplicació de la regla de les 20 H per reduir les EMI

La regla de les 20 H ajuda a reduir EMI en dissenys ràpids de PCB. Significa reduir el pla de potència 20 vegades l'alçada de la capa entre els plans de potència i de terra. Això redueix les emissions de RF a freqüències més baixes.

Estudiar | Troballes |

|---|---|

Estudi de la Universitat de Clemson | Seguint la regla de les 20-H, es redueixen les emissions de RF per sota de 300 MHz en ~5 dBμV/m. |

Juntes de proves universitàries | Les proves van mostrar que la regla de les 20 H va empitjorar EMI que els plans d'alimentació i de terra a ras. |

La regla de les 20 H funciona millor per a freqüències més baixes. A freqüències més altes, pot fer que EMI pitjor. Per a PCB ràpides, comproveu si la regla de les 20 H s'adapta a les vostres necessitats. De vegades, mantenir els plans d'alimentació i de terra alineats funciona millor.

Consell: Posa a prova el teu Disseny de PCB en condicions reals per trobar la millor manera de reduir EMI.

Consideracions de disseny a nivell de component

Optimització de la capacitat de filtratge

Els condensadors de filtratge són importants per mantenir els senyals clars en les plaques de circuits impresos ràpides. Trieu condensadors que coincideixin amb les freqüències necessàries per al vostre disseny. Ajuden a eliminar el soroll i a mantenir el voltatge estable per a un millor rendiment.

Per millorar el filtratge, centreu-vos en on i com feu servir els condensadors. Col·loqueu-los a prop dels pins d'alimentació per reduir els efectes no desitjats. Feu servir condensadors petits i grans per gestionar diferents freqüències. Per exemple, utilitzar condensadors de 0.1 µF i 10 µF junts pot bloquejar el soroll d'alta freqüència i estabilitzar les freqüències més baixes.

Els dissenys ràpids sovint utilitzen interfícies com ara USB, DDR, PCIe i Ethernet. Aquestes necessiten un control exacte de la impedància per enviar les dades correctament. Manipuleu les peces de terminació amb cura i establiu regles per als senyals d'alta velocitat. L'encaminament amb impedància controlada manté els senyals clars i forts.

L'eina d'integritat del senyal troba xarxes amb possibles problemes de reflexió. Mesura les formes d'ona directament, cosa que us ajuda a millorar el disseny per obtenir millors resultats.

No hi ha regles fixes per al disseny ràpid de PCB, però les bones pràctiques ajuden molt. Les eines de prova i simulació poden comprovar les opcions de condensadors i millorar la claredat del senyal.

Paper de l'embalatge de silici en el disseny de PCB d'alta velocitat

L'encapsulat de silici afecta la qualitat del senyal en dissenys de PCB ràpids. La xarxa d'alimentació de l'encapsulat actua com una barreja de condensadors i inductors. Això canvia la manera com gestiona els polsos elèctrics ràpids, cosa que afecta el rendiment de la PCB.

La impedància de potència del xip és clau per a la qualitat de la potència i del senyal. Està estretament relacionada amb la claredat del senyal, especialment a altes freqüències. A mesura que els xips funcionen a velocitats de GHz, la impedància de la xarxa elèctrica canvia. Això altera la qualitat del senyal i el rendiment general.

Descripció de l'evidència | Impacte en la integritat del senyal |

|---|---|

La xarxa elèctrica del paquet actua com a condensadors i inductors | Canvia la velocitat de gestió dels polsos, cosa que afecta el rendiment de la PCB |

La impedància de potència del xip afecta la qualitat de l'energia | Fortament vinculat a la claredat del senyal en dissenys d'alta freqüència |

Canvis d'impedància amb circuits de velocitat GHz | Altera la qualitat del senyal i afecta el rendiment |

Per millorar l'embalatge de silici, estudieu-ne les característiques elèctriques i com funciona amb la PCB. Utilitzeu eines de simulació per comprovar la impedància i trobar problemes. La solució d'aquests problemes millora la qualitat del senyal i fa que la vostra PCB funcioni millor en dissenys ràpids.

Gestió d'EMI i corrents de mode comú

Comprensió dels corrents de mode diferencial i de mode comú

En dissenys ràpids de PCB, els corrents de mode diferencial i de mode comú actuen de manera diferent. Els corrents de mode diferencial transporten dades entre els camins del senyal i de retorn. Els corrents de mode comú es produeixen a causa de desequilibris de circuits i flux en camins no desitjats. Aquests sovint causen EMI.

Els camins de senyal irregulars poden augmentar el soroll de mode comú i EMI. Per exemple:

La desigual separació entre les vies de terra i de senyal provoca una conversió de mode.

Els parells diferencials mal adaptats poden crear fins a -40 dB de soroll.

La investigació mostra que mantenir la simetria en els senyals redueix EMI per 80 dB.

Els parells diferencials ajuden a reduir EMI i bloquegen el soroll. Equilibren els senyals, cosa que és clau per a dissenys ràpids. Centreu-vos en dissenys simètrics i bones vies de retorn per controlar els corrents de mode comú.

Tècniques per minimitzar la radiació de corrent de mode comú

Reduir la radiació de corrent de mode comú manté els senyals forts en les plaques de circuits impresos ràpides. Proveu aquests mètodes:

Millora l'encaminament diferencial de parells: Feu coincidir les longituds de les traces i manteniu l'espaiat uniforme.

Col·loqueu bé les vies de terraCol·loqueu les vies de terra a prop de les vies de senyal per aturar la conversió en mode.

Utilitzeu la terminació adequadaAdapta la impedància als extrems per evitar reflexions.

Les proves mostren que aïllar els corrents de mode comú és important. Mitjançant sondes, els investigadors van mesurar aquests corrents col·locant cables dins de la sonda. Això va ajudar a estudiar EMI i models FDTD coincidents.

Tècnica de mesura | Què fa | Resultats |

|---|---|---|

Mesura de corrent en mode comú | Utilitza sondes per mesurar corrents de camp proper. | EMI els resultats coincidien amb els models FDTD. |

Mesura de corrent en mode diferencial | Mesura els corrents totals en diferents configuracions. | Resultats mostrats en valors relatius de dBµV. |

Les normes de la FCC limiten els corrents de mode comú per als productes de classe A i B. A 30 MHz, els productes de classe A han de mantenir-se per sota dels 24 µA i els de classe B per sota dels 8 µA.

Seguir aquestes regles i millorar el disseny de la PCB pot reduir la radiació de mode comú i augmentar el rendiment.

Estratègies de blindatge i connexió a terra per a la reducció d'EMI

El blindatge i la connexió a terra són maneres excel·lents de reduir EMI en plaques de circuits impresos ràpides. La connexió a terra proporciona als corrents no desitjats un camí de baixa resistència. El blindatge impedeix que els camps electromagnètics entrin o surtin de la placa de circuits impresos.

Per protegir eficaçment:

Utilitzeu cobertes metàl·liques o recobriments conductors a les peces sensibles.

Afegiu plans de terra sota línies de senyal ràpid per absorbir EMI.

Assegureu-vos que les connexions a terra siguin contínues per evitar que els espais en blanc actuïn com a antenes.

Una bona connexió a terra crea camins de retorn forts per als corrents de mode diferencial. Les vies de terra desiguals poden causar una conversió de mode i augmentar EMIEls estudis mostren que els dissenys simètrics poden tallar EMI per 60 dB.

Per a PCB ràpides, combineu blindatge i connexió a terra per reduir EMIAquests mètodes milloren la qualitat del senyal i compleixen els estàndards reglamentaris.

Consells avançats per al disseny de PCB d'alta velocitat

Ús de plans de referència i traces d'impedància controlada

Per mantenir els senyals clars en dissenys ràpids, utilitzeu plans de referència. Les traces d'impedància controlada també són importants. Si la impedància canvia, els senyals poden rebotar. Això debilita les dades i provoca errors. Els plans de terra i d'alimentació ajuden a que els senyals tornin suaument i més baix. EMI.

Quan feu el traçat, manteniu els traços curts i eviteu angles pronunciats. Els girs pronunciats poden confondre els senyals i augmentar EMIFeu servir corbes suaus o angles de 45 graus. Un bon encaminament de traçat i uns plans de referència forts fan que els senyals siguin més nets i millorin el rendiment.

Consell: Utilitzeu eines de simulació per comprovar la impedància i trobar punts problemàtics.

Minimitzar les vies i escurçar les longituds de les traces

Les pistes més curtes i menys vies són millors per a les PCB ràpides. Les pistes curtes redueixen els retards del senyal i eviten els desajustos d'impedància. Mantingueu les longituds de les pistes inferiors a 2 polzades per obtenir els millors resultats. Això manté els senyals forts i fiables.

Descripció de l'evidència | Insight clau |

|---|---|

Els traços més curts són millors. | Redueixen el retard del senyal i les desajustos d'impedància. |

Els traços de menys de 2 polzades funcionen millor. | Les traces curtes redueixen els retards i els problemes de desajustaments. |

Col·loqueu les vies a prop les unes de les altres. | Les vies agrupades milloren la conductivitat i redueixen les pèrdues resistives. |

Col·loca les vies a prop les unes de les altres per millorar el flux del senyal. Això redueix la resistència i augmenta el rendiment. No utilitzis massa vies, ja que poden causar efectes no desitjats.

Execució de senyals d'alta freqüència a les capes internes

Poseu els senyals d'alta freqüència a les capes internes per obtenir millors resultats. Les capes internes escurcen els camins del senyal. Això redueix els retards i evita el rebot del senyal. Les vies més petites també redueixen problemes com ara talls i impedància desajustada.

Els plans de potència i de terra de les capes internes ajuden encara més. Redueixen el soroll i la diafonia, donant als senyals un camí suau. Aquests plans també bloquegen EMI reduint el rebot del terra i el soroll de potència.

Nota: La configuració de la capa de la PCB afecta la impedància. Coses com l'amplada de la traça, el tipus de material i la distància als plans importen molt.

Dissenya les capes de la teva PCB amb cura. Això millora la intensitat del senyal i fa que els dissenys ràpids funcionin millor.

Per millorar els senyals en dissenys ràpids de PCB, planifica amb cura. Pots millorar enrutant bé les pistes, utilitzant bons materials i controlant les EMI. Per exemple, les xarxes 5G funcionen millor amb blindatges EMI forts i bons dissenys de pistes. De la mateixa manera, els dispositius es mantenen elegants i redueixen les EMI filtrant els senyals i enrutant-los intel·ligentment.

Un pla complet ajuda al teu circuit a funcionar bé en totes les situacions. Si tries els materials adequats, fas un encaminament precís i afegeixes bons blindatges, el teu circuit pot assolir els seus objectius. Fes servir aquests consells per millorar el teu disseny i obtenir grans resultats cada vegada.

FAQ

Què és el més important per a la integritat del senyal en dissenys ràpids de PCB?

Triar els materials adequats és molt important. Trieu materials amb una constant dielèctrica baixa (Dk) i tangent de pèrdues (Df) per mantenir els senyals clars. Aquestes característiques ajuden a reduir la pèrdua de senyal i a millorar el rendiment en dissenys d'alta velocitat.

Com es pot reduir l'EMI en dissenys ràpids de PCB?

Podeu reduir les EMI utilitzant blindatges, connexió a terra i bones rutes de traçat. Col·loqueu els plans de terra sota les línies de senyal i eviteu girs de traçat pronunciats. La regla de les 20 H per als plans d'alimentació ajuda a reduir les EMI a freqüències més baixes.

Per què és millor utilitzar menys vies en dissenys ràpids de PCB?

Les vies poden causar retards i desajustos de senyal. L'ús de menys vies manté el flux de senyals suau i evita problemes com les reflexions. Agrupar les vies juntes millora el flux del senyal i redueix la resistència.

Com ajuden els parells diferencials a la integritat del senyal?

Els parells diferencials mantenen els senyals equilibrats, reduint el soroll i les interferències electromagnètiques (EMI). Transporten corrents oposats que cancel·len les interferències. La coincidència de les longituds i l'espaiat de les traces fa que funcionin encara millor.

Poden les eines de simulació millorar la integritat del senyal?

Sí, les eines de simulació troben problemes com ara impedància i reflexions desajustades. Permeten provar els dissenys abans de fer-los, millorant el rendiment i la fiabilitat en PCB ràpides.

Consell: Prova eines com Altium Designer o Cadence per a millors simulacions.