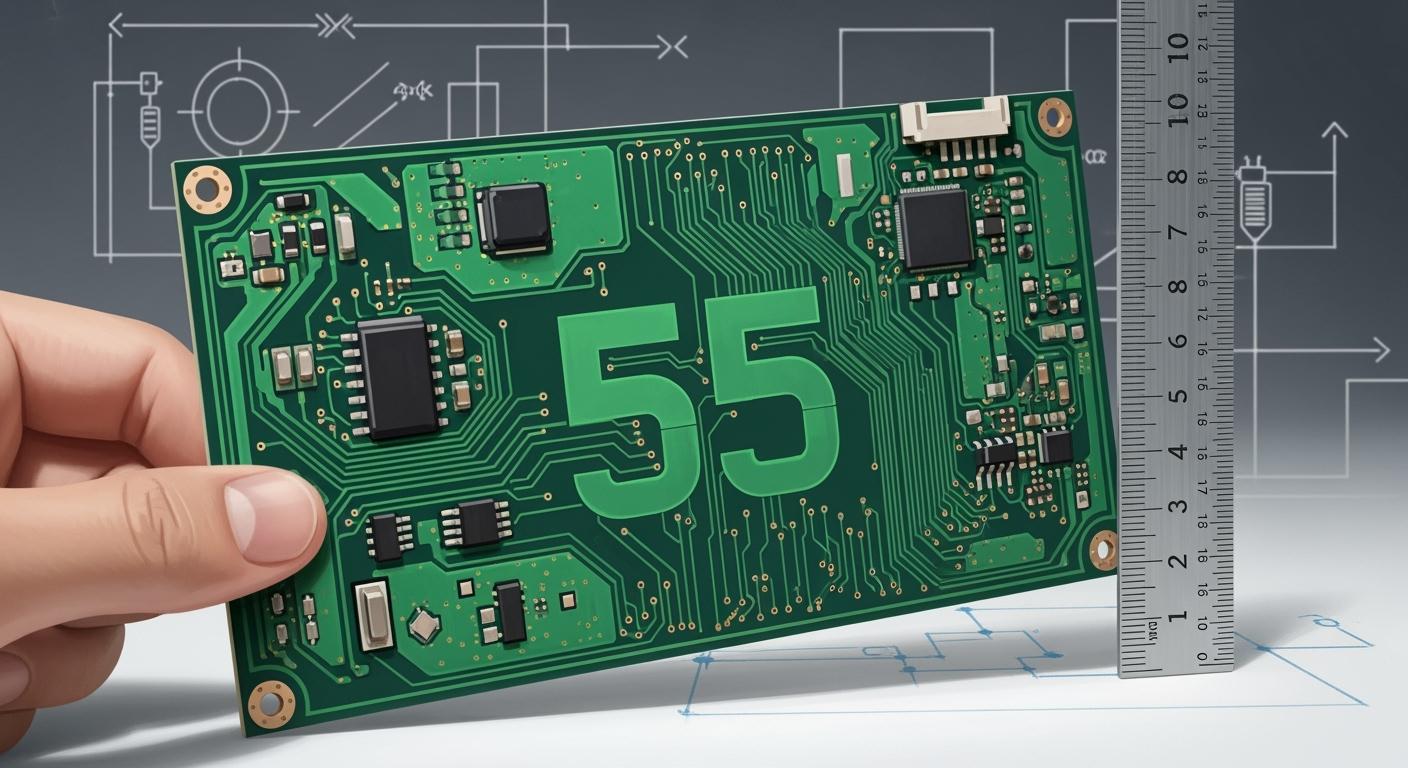

Anjeun nganggo aturan 55 dina desain PCB pikeun ngajaga jarak sinyal anjeun sahenteuna lima kali lébarna. Prakték ieu paling penting dina sirkuit kecepatan tinggi. Anjeun ningkatkeun integritas sinyal sareng ngirangan masalah sapertos EMI sareng crosstalk nalika anjeun nuturkeun aturan ieu. Anjeun kéngingkeun sinyal anu langkung bersih sareng kinerja anu langkung dipercaya.

Takeaways Key

Aturan 55 nyebatkeun pikeun ngajaga jarak antara tanda sinyal sahenteuna lima kali lébarna. Ieu ngabantosan sinyal tetep kuat sareng ngirangan gangguan.

Jieun jalur anu leuwih lega pikeun sinyal kecepatan tinggi pikeun nurunkeun résistansi. Ieu ngajaga sinyal tetep kuat sareng nyegah noise ngaganggu cara kerjana.

Jaga jarak anu gancang tetep pondok sareng ulah nganggo juru anu seukeut. Ieu ngirangan leungitna sinyal sareng masihan sinyal anjeun jalur anu langkung bersih.

Anggo alat simulasi pikeun mariksa desain anjeun sateuacan anjeun ngadamelna. Ieu bakal mendakan masalah ti mimiti sareng ngajantenkeun desain langkung saé.

Ngobrol sareng produsén PCB anjeun ngeunaan naon anu tiasa dilakukeun ku aranjeunna. Nyaho wates aranjeunna ngabantosan anjeun ngarancang hal anu cocog pikeun aranjeunna.

55 Tinjauan Aturan dina Desain PCB

Naon Ari Aturan 55?

Anjeun nganggo aturan 55 pikeun ngabantosan ngatur rohangan sareng ukuran tilas dina PCB. Aturan ieu nyebatkeun pikeun ngajaga tilas sahenteuna lima kali lébarna. Anjeun nuturkeun éta pikeun ngeureunkeun épék anu teu dihoyongkeun dina sirkuit kecepatan tinggi. Upami tilas jauh, sinyal moal silih campur. Sinyal tiasa pindah ti hiji tempat ka tempat anu sanés kalayan langkung gampang. Aturan 55 ngabantosan PCB anjeun tiasa dianggo kalayan saé pikeun sinyal anu gancang.

Dasar Téknis sareng Asalna

Anjeun kedah terang kunaon aturan 55 penting pikeun kualitas sinyal. Ide utama nyaéta pikeun ngontrol dimana sinyal ngurilingan sareng sabaraha lega sareng jauhna jarak antara jalur. Upami anjeun nganggo aturan 55, anjeun ngirangan masalah sapertos noise sareng lonjakan voltase. Anjeun ogé nyegah sinyal nyampur sareng jalur daya, anu tiasa nyababkeun kasalahan.

Tip: Aturan 55 tiasa ngajantenkeun PCB anjeun langkung saé, khususna upami nganggo sinyal anu gancang.

Tabél di handap ieu nunjukkeun ideu élmu anu ngadukung aturan 55 dina desain PCB:

dasar | katerangan |

|---|---|

Ngaminimalkeun Induktansi Parasit | Renik daya anu pondok ngajantenkeun area loop langkung alit, anu ngabantosan dina sirkuit di/dt anu luhur pikeun ngeureunkeun tegangan anu disada. |

Anggo Lapisan Luar pikeun Lacak Arus Tinggi | Lapisan luar leuwih tiis; ngagunakeun leuwih loba vias ngabantu ngurangan arus anu luhur. |

Nyegah Kopling Lacak Daya Sinyal | Lacak sinyal kedah meuntas lacak daya dina sudut katuhu pikeun ngeureunkeun kopling kapasitif sareng ngajaga sinyal tetep bersih. |

Unggal prinsip ngabantosan ngajaga sinyal tetep kuat sareng bersih. Anjeun nurunkeun induktansi parasit ku cara nyegah tilas tina ngulang teuing. Anjeun nganggo lapisan luar pikeun tilas arus tinggi pikeun ngabantosan panas sareng arus. Anjeun ngajaga tilas sinyal jauh tina tilas daya pikeun ngeureunkeun campuran anu teu dihoyongkeun. Léngkah-léngkah ieu sadayana ngabantosan aturan 55 jalan sareng masihan hasil anu langkung saé dina desain pcb kecepatan tinggi.

Pentingna pikeun Desain PCB Gancang

Dampak Integritas Sinyal

Anjeun kedah ngajaga sinyal anjeun tetep bersih sareng kuat dina desain PCB kecepatan tinggi. Aturan 55 ngabantosan anjeun ngalakukeun ieu ku cara mastikeun unggal jejak sinyal tetep cukup jauh ti anu sanés. Nalika anjeun nuturkeun aturan ieu, anjeun ngajantenkeun jalur sinyal pondok sareng langsung. Ieu ngajaga sinyal tina ngumpulkeun noise atanapi kaleungitan kakuatan. Anjeun ogé nyegah sinyal tina mantul deui sareng nyababkeun kasalahan.

Aturan 55 penting pisan pikeun desain PCB kecepatan tinggi sabab museur kana ngaminimalkeun area loop sinyal. Ieu paling penting nalika anjeun damel kalayan kecepatan clock anu luhur atanapi waktos naékna sinyal anu gancang. Area loop anu alit hartosna sinyal gaduh kasempetan anu langkung sakedik pikeun ngajemput noise anu teu dihoyongkeun. Anjeun kéngingkeun kinerja anu langkung saé tina PCB anjeun nalika anjeun nganggo aturan ieu.

Catetan: Jalur sinyal anu bersih hartosna masalah anu langkung sakedik sareng sirkuit anu langkung tiasa diandalkeun.

Pangurangan EMI sareng Crosstalk

Anjeun hoyong nyingkahan masalah sapertos EMI sareng crosstalk dina PCB anjeun. EMI nangtung pikeun gangguan éléktromagnétik. Crosstalk kajadian nalika hiji sinyal mangaruhan sinyal caket anu sanés. Duanana tiasa nyababkeun sirkuit anjeun gagal atanapi bertindak ku cara anu anéh.

Anjeun tiasa nganggo aturan 55 pikeun ngirangan résiko ieu. Nalika anjeun misahkeun tilas, anjeun ngirangan kasempetan yén hiji sinyal bakal luncat ka tilas anu sanés. Anjeun ogé ngajantenkeun langkung sesah pikeun bising luar pikeun lebet kana sinyal anjeun. Ieu ngajantenkeun desain PCB kecepatan tinggi anjeun langkung dipercaya.

Ieu sababaraha kauntungan anu anjeun kéngingkeun nalika anjeun nuturkeun aturan 55:

Résiko kasalahan sinyal anu langkung handap

Langkung sakedik reset atanapi gangguan acak

kinerja sakabéh hadé

Anjeun ningkatkeun desain anjeun ku cara ngajaga sinyal tetep misah sareng kuat. Ieu ngarah kana PCB anu tiasa dianggo kalayan saé, bahkan dina kecepatan anu luhur.

Nerapkeun Aturan 55 dina Tata Letak PCB

Pedoman Lebar sareng Spasi Lacak

Anjeun kedah milih lébar sareng jarak trace anu pas. Aturan 55 nyebatkeun trace kedah lima kali lébarna. Ieu ngajaga unggal sinyal aman tina noise sareng gangguan. Pikeun sinyal anu gancang, anggo trace anu langkung lega pikeun ngirangan résistansi. Trace anu langkung lega ngabantosan ngajaga sinyal tetep kuat. Bagian anu alit peryogi sahenteuna 0.5 mm rohangan. Bagian anu langkung ageung peryogi 1-2 mm rohangan. Pamariksaan aturan desain ngabantosan anjeun mendakan kasalahan jarak.

Tip: Coba arahkeun jalur dina sudut 45 derajat. Ieu ngajantenkeun jalur sinyal langkung lancar sareng ngeureunkeun pantulan.

Tabél basajan tiasa ngabantosan anjeun nginget naon anu kedah dilakukeun:

Jenis ngalacak | Dianjurkeun Width | Spasi Minimum (aturan 55) |

|---|---|---|

Sinyal kecepatan tinggi | 0.2 mm | 1.0 mm |

Lacak kakuatan | 0.5 mm | 2.5 mm |

Sinyal analog | 0.2 mm | 1.0 mm |

Strategi Tumpukan Lapisan

Anjeun tiasa nganggo langkung seueur lapisan dina PCB anjeun pikeun ngabantosan sinyal. Pasangkeun bidang taneuh gigireun lapisan sinyal kecepatan tinggi. Ieu ngirangan noise sareng ngajaga sinyal tetep bersih. Jaga sinyal analog sareng digital dina lapisan anu béda. Ieu ngeureunkeun crosstalk sareng ngajantenkeun desain anjeun langkung saé. Anggo tilas anu lega dina lapisan daya pikeun aliran daya anu saé. Pasang bagian-bagian anu peryogi daya anu sami babarengan.

Catetan: Salawasna jieun panjang trace sami pikeun pasangan diferensial. Ieu ngajaga sinyal tetep cocog.

Praktik Pangsaéna pikeun Routing Sinyal

Anjeun kedah ngarutekeun sinyal sacara saksama dina PCB anjeun. Jaga jalur kecepatan tinggi tetep pondok sareng lempeng. Entong nganggo juru anu seukeut sabab ngarusak sinyal. Anggo alat simulasi pikeun mariksa masalah. Simpen bagian anu panas jauh tina jalur sinyal anu penting. Anggo via termal pikeun mindahkeun panas tina titik-titik konci.

Ieu sababaraha kasalahan sareng kumaha carana nyingkahanana:

Jarak bagian anu salah: Anggo pamariksaan aturan desain.

Perutean jejak anu goréng: Jaga lébar jejak tetep sami sareng anggo sudut 45 derajat.

Moal hilap integritas sinyal: Anggo bidang taneuh sareng cocogkeun panjang tapak.

Aliran daya anu lemah: Anggo jalur anu lega sareng kelompokkeun bagian anu sami.

Henteu nanganan panas: Anggo vias termal sareng panempatan bagian anu cerdas.

Aturan manufaktur anu leungit: Turutan aturan desain standar.

Anjeun tiasa ngajantenkeun PCB anjeun kuat sareng tiasa diandelkeun upami anjeun nuturkeun léngkah-léngkah ieu. Aturan 55 ngabantosan ngajaga sinyal tetep bersih sareng desain anjeun aman.

Tangtangan dina Desain PCB Gancang

Penempatan Komponen Padet

Anjeun bakal nyanghareupan seueur tantangan nalika anjeun nyobian ngajaga aturan 55 dina PCB kecepatan tinggi. Penempatan komponén anu padet ngajantenkeun hésé pikeun ngajaga rohangan anu cekap antara tilas. Anjeun tiasa ningali langkung seueur cacad solder nalika bagian-bagianna caket teuing. Ieu tiasa nyababkeun langkung seueur padamelan ulang sareng perbaikan. Anjeun ogé résiko sambungan anu lemah upami sababaraha bagian ngahalangan panas nalika nyolder. Papan kalayan jarak anu langkung saé langkung awét sareng nanganan langkung seueur siklus termal sateuacan gagal.

Tata letak anu heureut tiasa ningkatkeun pengerjaan ulang ku 37% kusabab masalah patri.

Bagian anu jangkung tiasa nimbulkeun kalangkang termal, nyababkeun sambungan anu lemah anu pegat nalika tés setrés.

Jarak anu saé ngabantosan papan anjeun tahan tilu kali langkung lami siklus pemanasan sareng pendinginan.

Anjeun kedah teras ngarencanakeun desain anjeun pikeun masihan unggal sinyal rohangan anu cekap. Ieu ngabantosan papan anjeun tetep kuat sareng tiasa dipercaya.

Ngatur Pasangan Diferensial

Anjeun kedah ati-ati dina ngarutekeun pasangan diferensial dina desain sinyal kecepatan tinggi. Pasangan diferensial mawa dua sinyal anu kedah tetep caket sareng cocog panjangna. Upami anjeun teu tiasa ngajaga jarak anu pas, anjeun tiasa kaleungitan kualitas sinyalAnjeun kedah ngajaga jarak antara dua jalur éta alit, tapi ogé ngajaga sinyal anu sanés tetep jauh. Ieu ngabantosan anjeun nyingkahan crosstalk sareng ngajaga sinyal kecepatan tinggi anjeun tetep bersih.

Coba anggo papan multi-lapisan pikeun misahkeun lapisan sinyal sareng bidang taneuh. Ieu masihan anjeun langkung seueur kontrol kana jalur jejak sareng ngabantosan anjeun nuturkeun aturan 55. Salawasna pariksa yén duanana jejak dina pasangan gaduh panjang anu sami. Ieu ngajaga sinyal anjeun saimbang.

Ngalawan Watesan Manufaktur

Anjeun tiasa waé ngalaman wates anu ditetepkeun ku produsén pcb anjeunSababaraha pabrik teu tiasa ngadamel tilas anu ipis pisan atanapi sela-sela anu alit pisan. Ieu tiasa ngajantenkeun hésé nuturkeun aturan 55, khususna dina desain kecepatan tinggi. Anjeun kedah ngobrol sareng produsén anjeun dina awal prosés. Tanyakeun ngeunaan lébar tilas minimum sareng jarakna. Anggo papan multi-lapisan upami anjeun peryogi langkung seueur rohangan pikeun perutean sinyal kecepatan tinggi.

Tip: Salawasna pariksa aturan desain anjeun sateuacan anjeun ngarengsekeun tata letak anjeun. Ieu ngabantosan anjeun nyingkahan parobihan anu mahal engké.

Anjeun tiasa ngarengsekeun seueur masalah ku cara ngarencanakeun sateuacanna sareng damel sareng produsén anjeun. Ieu ngajaga sinyal kecepatan tinggi anjeun tetep kuat sareng papan anjeun tiasa diandelkeun.

Ngaoptimalkeun Kinerja PCB nganggo Aturan 55

Tip Tata Letak sareng Routing

Anjeun tiasa ngajantenkeun PCB anjeun langkung saé ku cara nganggo tata letak sareng routing anu cerdas. Nempatkeun bagian-bagian dina tempat anu saé ngabantosan anjeun ngalereskeun masalah langkung gancang sareng ngahémat artos. Retakan pondok ngabantosan sinyal tetep kuat sareng ngeureunkeun gangguan. Jarak anu cekap antara retakan nyegah sinyal nyampur sareng janten lemah. Nganggo lébar retakan anu sami ngabantosan ngontrol impedansi sareng ngeureunkeun turunna tegangan. Upami anjeun ngarutekeun sinyal penting heula, desain anjeun tiasa dianggo langkung saé sareng langkung dipercaya.

Simpen bagian-bagianna di tempat anu cerdas supados langkung gampang dipasangna.

Anggo jalur pondok pikeun ngajaga sinyal tetep kuat.

Bere jarak antara jalur pikeun nyegah masalah sinyal.

Jaga lébar lajur tetep sami pikeun impedansi anu saé.

Rutekeun heula sinyal konci pikeun nyingkahan masalah engké.

Tip: Jieun jalur sinyal kecepatan tinggi pondok sareng langsung.

Simulasi jeung Validasi

Anjeun kedah teras-terasan mariksa desain anjeun nganggo alat simulasi sateuacan ngadamel PCB anjeun. Seueur alat anu gaduh langkung ti 100 aturan, sapertos aturan 55, pikeun ngabantosan anjeun mendakan masalah langkung awal. Mesin anu gancang ngamungkinkeun anjeun mariksa masalah gancang. Anjeun tiasa ngalalaworakeun alarm palsu pikeun ngahémat waktos sareng fokus kana masalah nyata. Panyaringan anu langkung saé ngamungkinkeun anjeun ngadamel daptar pikeun mariksa sinyal penting. Alat pamotongan daérah ngabantosan anjeun ningali bagian-bagian alit tina desain anjeun pikeun pamariksaan anu langkung saé.

hal nu husus | gambaran |

|---|---|

Aturan anu tos ditetepkeun | Leuwih ti 100 aturan pikeun kabutuhan desain anu béda, kaasup aturan 55. |

Mesin Tertanam anu Éfisién | Seueur mesin mariksa masalah kalayan gancang. |

Manajemén Palanggaran Palsu | Ulah ngadéngékeun alarm palsu pikeun ngahémat waktos. |

Kamampuh Nyaring Anu Ditingkatkeun | Jieun daptar pikeun mariksa sinyal-sinyal penting. |

Fungsi Tanaman Luas | Tingali daérah desain anu alit pikeun pamariksaan anu langkung saé. |

Catetan: Anggo alat simulasi pikeun mariksa jalur sinyal sareng jarak sateuacan ngadamel PCB anjeun.

Damel sareng Pabrikator

Anjeun tiasa ngajantenkeun PCB anjeun langkung saé ku cara damel sareng pabrikator anjeun. Microvias anu disusun langkung mirah sareng ngajantenkeun papan anjeun langkung kuat tibatan microvias anu ditumpuk. Ngeusian vias anu kosong nyegah cai asup sareng nyegah karusakan papan. Nganggo langkung seueur microvias dina bantalan termal QFN ngabantosan aliran solder sareng ngeureunkeun masalah nalika dipanaskeun. Ngajaga rohangan di sisi ngajaga papan anjeun aman nalika motong.

Pilih microvias anu disusun bertingkat pikeun papan anu langkung kuat.

Eusian vias kosong supaya cai teu asup.

Anggo langkung seueur microvias dina bantalan termal pikeun patri anu saé.

Jaga rohangan di sisi pikeun ngajaga papan anjeun nalika motong.

Tip: Ngobrol sareng pabrik anjeun ti heula pikeun mastikeun desain anjeun ngadukung sinyal kecepatan tinggi anu kuat.

Anjeun kéngingkeun integritas sinyal anu langkung saé sareng kirang kasalahan nalika anjeun nganggo aturan 55 dina desain PCB kecepatan tinggi. Aturan ieu ngabantosan anjeun nurunkeun EMI sareng crosstalk. Sirkuit anjeun tiasa dianggo langkung dipercaya. Pikeun ngajantenkeun desain PCB anjeun langkung saé, cobian ideu ieu:

make manajemen kendala pikeun ngabantosan ngarencanakeun desain anjeun.

Anggo desain anu parantos tiasa dianggo kalayan saé pikeun ngahémat waktos sareng nyingkahan masalah.

Anggo otomatisasi pikeun nyiapkeun file pikeun diproduksi sareng ningkatkeun kualitas.

Terus diajar hal-hal anyar sareng sering latihan pikeun ngadamel PCB anu langkung saé unggal waktos.

FAQ

Naon hartina aturan 55 dina desain PCB?

Anjeun nganggo aturan 55 pikeun ngajaga unggal tilas sinyal sahenteuna lima kali lébarna tina tilas anu sanés. Ieu ngabantosan anjeun ngirangan noise sareng gangguan dina sirkuit anjeun.

Naha anjeun tiasa nganggo aturan 55 pikeun sadaya desain PCB?

Anjeun kedah nganggo aturan 55 pikeun sinyal kecepatan tinggi atanapi sénsitip. Pikeun sirkuit kecepatan rendah atanapi sirkuit saderhana, anjeun panginten henteu peryogi jarak anu lega sapertos kitu. Salawasna parios heula kabutuhan desain anjeun.

Kumaha aturan 55 ngabantosan EMI?

Anjeun nurunkeun gangguan éléktromagnétik (EMI) nalika anjeun ngajaga tilas jarak anu jauh. Aturan 55 ngajantenkeun sinyal langkung sesah luncat antara tilas. Ieu ngajaga sirkuit anjeun tetep bersih sareng tiasa dipercaya.

Kumaha upami produsén PCB anjeun henteu tiasa minuhan aturan 55?

Anjeun kedah ngobrol sareng produsén anjeun ti payun. Tanyakeun ngeunaan lébar sareng jarak minimumna. Upami aranjeunna henteu tiasa nyumponan aturan 55, anjeun panginten kedah nyaluyukeun desain anjeun atanapi nganggo langkung seueur lapisan.